2.6. Таймеры/счетчики

В AT90S2313 предусмотрены два таймера/счетчика общего назначения: 8-разрядный и 16-разрядный. Каждый из таймеров индивидуально подключается к одному из выходов 10-разрядного предварительного делителя частоты. Оба таймера могут использоваться как таймеры с внутренним источником импульсов или как счетчики импульсов, поступающих извне.

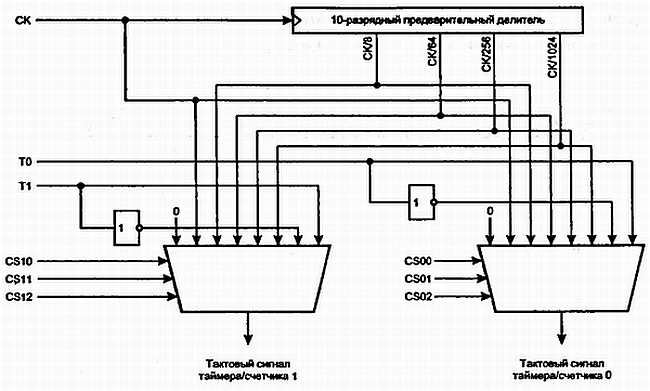

В качестве источника импульсов для таймеров можно выбрать сигнал тактовой частотой микроконтроллера (СК), импульсы предварительного делителя (СК/8, СК/64, СК/256 или СКУ1024) или импульсы с соответствующего внешнего вывода. На рис. 2.25 изображена структурная схема предварительного делителя частоты.

Кроме того, таймеры могут быть остановлены.

Рис. 2.25. Предварительный делитель тактовой частоты для таймеров

8-разрядный таймер/счетчик 0

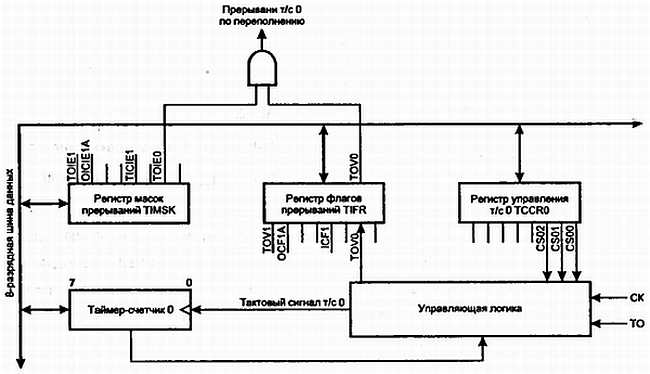

8-разрядный таймер/счетчик может получать импульсы тактовой частоты — СК, импульсы с предварительного делителя (СК/8, СК/64, СК/256 или СК/1024), импульсы с внешнего вывода или быть остановлен соответствующими установками регистра TCCR0. Флаг переполнения таймера находится в регистре TIFR. Биты управления таймером расположены в регистре TCCR0. Разрешение и запрещение прерываний от таймера управляется регистром TIMCK.

При работе таймера/счетчика от внешнего сигнала этот сигнал синхронизируется с тактовым генератором микроконтроллера. Для правильной обработки внешнего сигнала минимальное время между соседними импульсами должно превышать период тактовой частоты процессора. Сигнал внешнего источника обрабатывается по спадающему фронту тактовой частоты процессора.

Рис. 2.26. Блок-схема таймера/счетчика 0

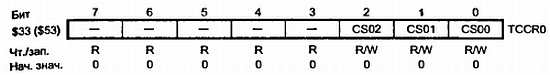

Рис. 2.27. Регистр управления таймером/счетчиком 0 TCCR0

Биты 7…3 — в AT90S2313 зарезервированы и всегда читаются как 0.

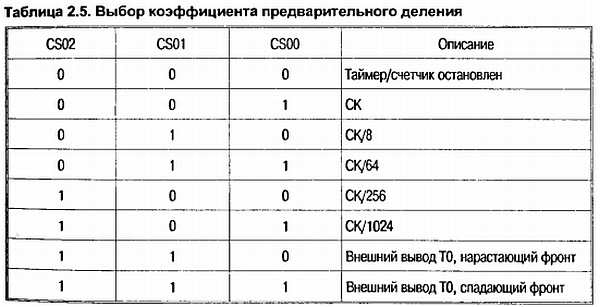

Биты 2, 1, 0 — CS02, CS01, CS00 — выбор тактовой частоты. Эти биты задают коэффициент деления предварительного делителя.

Условие «Таймер/счетчик остановлен» запрещает или разрешает функционирование таймера/счетчика. В режимах деления используется частота тактового генератора микроконтроллера. При работе от внешнего источника предварительно должен быть установлен соответствующий бит регистра направления данных.

Рис. 2.28. Таймер/счетчик 0 TCNT0

Таймер/счетчик реализован как нарастающий счетчик с возможностью чтения и записи. При записи таймера/счетчика, если присутствуют тактовые импульсы, таймер/счетчик продолжает счет в следующем за операцией записи тактовом цикле таймера.

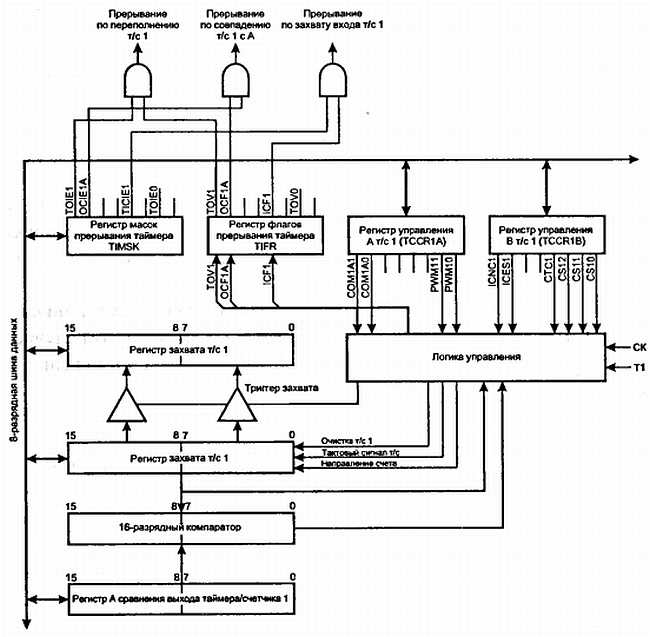

16-разрядный таймер/счетчик 1

16-разрядный таймер/счетчик может получать импульсы тактовой частоты — СК, импульсы с предварительного делителя (СК/8, СК/64, СК/256 или СК/1024), импульсы с внешнего вывода или быть остановлен соответствующими установками регистра TCCR1A. Флаги состояния таймера (переполнения, совпадения и захвата) и управляющие сигналы находятся в регистре TIFR. Разрешение и запрещение прерываний от таймера 1 управляется регистром TIMCK.

Рис. 2.29. Блок-схема таймера/счетчика 1

При работе таймера/счетчика 1 от внешнего сигнала этот сигнал синхронизируется с тактовым генератором микроконтроллера. Для правильной обработки внешнего сигнала минимальное время между соседними импульсами должно превышать период тактовой частоты процессора. Сигнал внешнего источника обрабатывается по спадающему фронту тактовой частоты процессора.

Таймер/счетчик 1 поддерживает функцию совпадения, используя регистр совпадения OCR1А в качестве источника для сравнения с содержимым счетчика. Функция совпадения поддерживает очистку счетчика и переключение выхода по совпадению.

Таймер/счетчик 1 можно использовать как 8-, 9- или 10-разрядный широтно-импульсный модулятор (ШИМ). В этом режиме счетчик и регистр OCR1 работают как защищенный от дребезга независимый ШИМ с отцентрованными импульсами. Подробнее эта функция будет описана ниже.

Функция захвата по входу предусматривает захват содержимого таймера/счетчика 1 в регистр захвата ICR1 и управляется внешним сигналом на входе захвата — ICP. Работа режима захвата определяется управляющим регистром TCCR1.

При работе захвата по входу может быть включена схема подавления шума, при этом сигнал захвата возникает только в том случае, если событие, управляющее захватом, наблюдается на протяжении 4 машинных циклов.

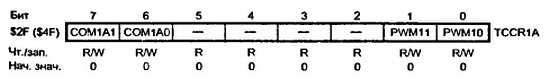

Рис. 2.30. Регистр А управления таймером/счетчиком 1 TCCR1A

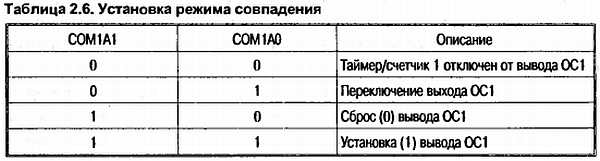

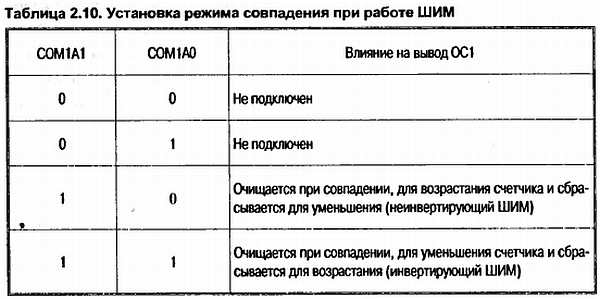

Биты 7, 6 — СОМ1А1, СОМ1А0: режим выхода совпадения, биты 1 и 0. Эти управляющие биты надают отклик вывода ОС 1 процессора на совпадение регистра сравнения и таймера/счетчика 1. Поскольку это апьтернативная функция пор га, соответствующий бит направления должен устанавливать вывод на выход. Конфигурация управляющих битов показана в следующей таблице.

В режиме ШИМ эти биты имеют другие функции, которые указаны в табл. 2.10.

При изменении битов СОМ1А1 и СОМ1А0 прерывание по совпадению должно быть запрещено очисткой соответствующего бита в регистре TIMCK. В противном случае прерывание может произойти во время изменения этих битов.

Биты 5…2 — в AT90S2313 зарезервированы и всегда читаются как 0.

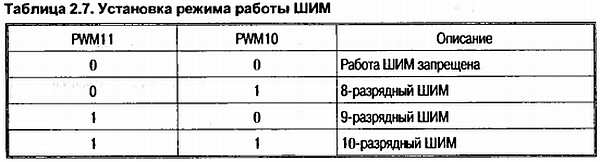

Биты 1,0 — PWM11, PWM10: биты установки ШИМ. Эти биты устанавливают режим работы таймера/счетчика 1 в качестве ШИМ (табл. 2.7). Подробнее этот режим будет рассмотрен ниже.

Рис. 2.31. Регистр управления таймером/счетчиком 1 TCCR1B

Бит 7 — ICNC1: подавитель входного шума входа захвата. Если ICNC1=0, подавление входного шума входа захвата запрещено. При этом захват срабатывает по первому заданному (нарастающему или спадающему) фронту сигнала на выводе ICP. При установке бита обрабатываются четыре последовательные выборки сигнала на выводе ICP. Для срабатывания захвата все выборки должны соответствовать уровню, заданному битом ICES1. Частота выборок равна тактовой частоте процессора.

Бит 6 — ICES1: выбор фронта сигнала захвата. Если бит ICES1 = 0, содержимое таймера/счетчика 1 переписывается в регистр захвата по спадающему фронту сигнала на выводе ICP. Если бит установлен — по нарастающему фронту сигнала.

Биты 5, 4 — в AT90S2313 зарезервированы и всегда читаются как 0.

Бит 3 — СТС1: очистка таймера/счетчика 1 по совпадению. Если бит СТС1 = 1, таймер/счетчик 1 устанавливается в $0000 в такте, следующем за событием совпадения. Если бит сброшен, таймер/счетчик 1 продолжает считать, пока не будет остановлен, сброшен, произойдет его переполнение или изменение направления счета. В режиме ШИМ этот бит не работает.

Биты 2, 1, 0 — CS12, CS11, CS10: выбор источника тактирования. Эти биты определяют источник счетных импульсов для таймера/счетчика 1.

Рис. 2.32. Таймер/счетчик 1 TCNT1H и TCNT1L

Это 16-разрядный регистр, содержащий текущее значение таймера/счетчика 1. Чтобы чтение и запись двух байтов счетчика происходило синхронно, для работы с ним используется временный регистр (TEMP).

Запись в таймер/счетчик 1: при записи старшего байта в TCNT1H записываемые данные помещаются в регистр TEMP. Затем, при записи младшего байта, он вместе с данными из TEMP переписывается в таймер/счетчик 1. Таким образом, при записи 16-разрядного значения первым должен записываться байт в TCNT1H;

Чтение таймера/счетчика 1: при чтении младшего байта из TCNT1L он посылается в процессор, а данные из TCNT1H переписываются в регистр TEMP, т. е. одновременно читаются все 16 разрядов. При последующем чтении регистра TCNT1H данные берутся из регистра TEMP.

Таймер/счетчик 1 организован как суммирующий счетчик (в режиме ШИМ — суммирующий/вычитающий) с возможностью чтения и записи. Если выбран источник тактовых импульсов для таймера/счетчика 1, после записи в него нового значения он продолжает счет в следующем после записи периоде тактовой частоты.

Рис. 2.33. Регистр совпадения А таймера/счетчика 1

Регистр совпадения — 16-разрядный регистр, доступный для чтения и записи.

В этом регистре хранятся данные, которые непрерывно сравниваются с текущим значением таймера/счетчика 1. Действие по совпадению задается регистрами управления таймером/счетчиком 1 и регистром состояния.

Поскольку регистр OCR1A 16-разрядный, при записи нового значения в регистр, для того чтобы оба байта регистра записывались одновременно, используется временный регистр. При записи старшего байта данные помещаются во временный регистр, который переписывается в OCR1АН при записи младшего байта в OCR1AL. Таким образом, для записи в регистр первым должен записываться старший байт.

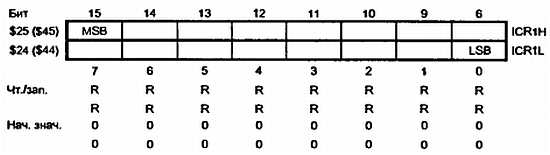

Рис. 2.34. Регистр захвата таймера/счетчика 1 — ICR1H и ICR1L

Регистр захвата — 16-разрядный регистр, доступный только для чтения. По нарастающему или спадающему фронту (в соответствии с выбором фронта импульса захвата ICES1) сигнала на выводе ICP текущее значение таймера/счетчика 1 переписывается в регистр захвата ICR1. В это же время устанавливается флаг захвата ICF1.

Поскольку регистр захвата является 16-разрядным, для чтения его значения, чтобы оба байта прочитались одновременно, используется временный регистр. При чтении младшего байта ICR1L старший байт регистра ICR1H переписывается во временный регистр. При чтении старшего байта он принимается из временного регистра. Таким образом, для чтения 16-разрядного регистра первым должен читаться младший байт.

Таймер/счетчик в режиме ШИМ

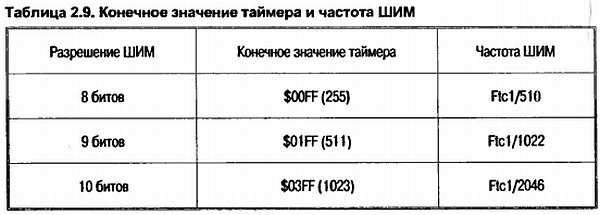

При выборе режима широтно-импульсной модуляции (ШИМ) таймер/счетчик 1 и регистр совпадения OCR1А формируют 8-, 9- или 10-разрядный непрерывный, свободный от «дрожания» и правильный по фазе сигнал, выводимый на вывод РВЗ(ОС1). Таймер/счетчик 1 работает как реверсивный счетчик, считающий от 0 до конечного значения (табл. 2.9).

При достижении конечного значения счетчик начинает считать в обратную сторону до нуля, после чего рабочий цикл повторяется. Когда значение счетчика совпадает с 8, 9 или 10 младшими битами регистра OCR1A, вывод PD1(OC1) устанавливается или сбрасывается в соответствии с установками битов СОМ1А1 и СОМ1А0 в регистре TCCR1 (табл. 2.10).

В режиме ШИМ при записи в регистр OCR1A 10 младших битов передаются во временный регистр и переписываются только при достижении таймером/счетчиком конечного значения. При этом устраняется появление несимметричных импульсов (дрожания), которые неизбежны при асинхронной записи OCR1A.

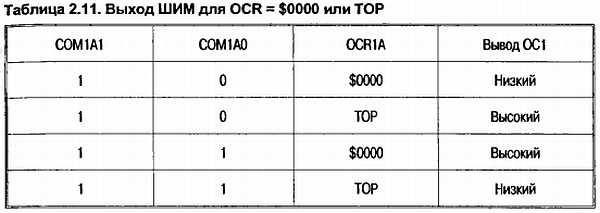

Если OCR1A содержит значение $0000 или конечное значение (ТОР), вывод ОС1 остается в том состоянии, которое определяется установками СОМ1А1 и СОМ1А0. Это показано в табл. 2.11.

В режиме ШИМ флаг переполнения таймера 1 (TOV1) устанавливается, когда счетчик изменяет направление счета в точке $0000. Прерывание по переполнению таймера 1 работает как при нормальном режиме работы таймера/счетчика, т. е. оно выполняется, если установлен флаг ТОV1 и разрешены соответствующие прерывания. То же самое касается флага совпадения и прерывания по совпадению.

Сторожевой таймер

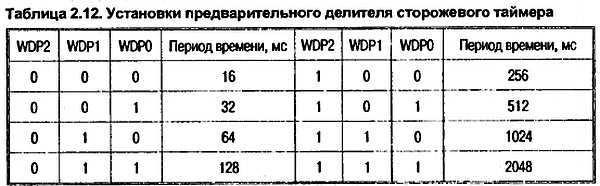

Сторожевой таймер работает от отдельного встроенного генератора, работающего на частоте 1 МГц (это типовое значение частоты для питания 5 В). Управляя предварительным делителем сторожевого таймера, можно задавать интервал сброса таймера от 16 до 2048 мс. Команда WDR сбрасывает сторожевой таймер. Для работы сторожевого таймера можно выбрать одно из восьми значений частоты, что позволяет в широких пределах изменять время между исполнением команды WDR и сбросом процессора. При отработке периода работы сторожевого таймера, если не поступила команда WDR, AT90S2313 сбрасывается, выполнение программы продолжается с вектора сброса.

Для предотвращения нежелательного отключения сторожевого таймера, для его запрещения должна выполняться определенная последовательность, которая описана при рассмотрении регистра WDTCR.

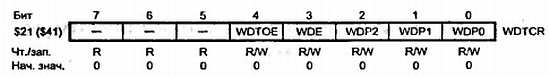

Рис. 2.35. Регистр управления сторожевым таймером — WDTCR

Биты 7…5 — в AT90S2313 зарезервированы и всегда читаются как 0.

Бит 4 — YVDTOE — разрешение выключения сторожевого таймера. При очистке бита WDE этот бит должен быть установлен, иначе работа сторожевого таймера не прекращается. Через четыре такта после установки этого бита он аппаратно сбрасывается.

Бит 3 — WDE — разрешение сторожевого таймера. Если бит установлен, работа сторожевого таймера разрешена, если бит сброшен — запрещена. Сброс бита производится только в том случае, если бит WDTOE установлен в 1.

Биты 2…0 — WDP2…0 — биты предварительного делителя сторожевого таймера. Если работа сторожевого таймера разрешена, эти биты определяют предварительный коэффициент деления для сторожевого таймера. В табл. 2.12 приведены различные значения установок предварительного делителя и соответствующие им временные интервалы при напряжении питания Vcc = 5 В.

Для запрещения включенного сторожевого таймера должна исполняться следующая процедура:

1. Одной командой записать 1 в WDTOE и WDE. Единица в WDE должна записываться даже в том случае, если этот бит был установлен перед началом процедуры остановки таймера.

2. В течение следующих четырех тактов процессора необходимо записать в WDE логический 0, при этом работа сторожевого таймера запрещается.

Более 800 000 книг и аудиокниг! 📚

Получи 2 месяца Литрес Подписки в подарок и наслаждайся неограниченным чтением

ПОЛУЧИТЬ ПОДАРОК