2.8. Универсальный асинхронный приемопередатчик

Микроконтроллер AT90S2313 имеет встроенный универсальный асинхронный приемопередатчик (UART).

Основные характеристики UART:

• генерация произвольных значений скорости;

• высокая скорость даже при низких тактовых частотах;

• 8 или 9 битов данных;

• фильтрация шума;

• определение переполнения;

• детектирование ошибки кадра;

• определение неверного стартового бита;

• три раздельных прерывания — завершение передачи, очистка регистра передачи и завершение приема.

Передача данных

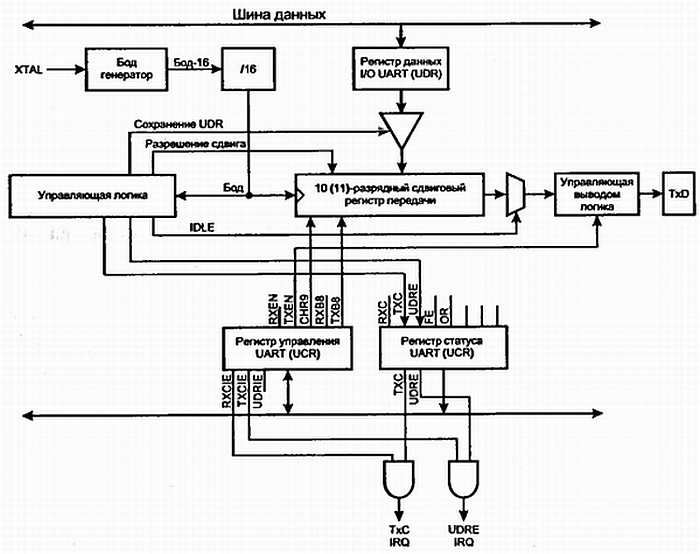

Структурная схема узла передачи данных UART показана на рис. 2.39.

Рис. 2.39. Структурная схема узла передачи данных UART

Передача данных инициируется записью передаваемых данных в регистр ввода/вывода данных UART — UDR. Данные пересылаются из UDR в сдвиговый регистр передатчика, когда:

• новый символ записывается в UDR после того, как был выдвинут стоповый бит для предыдущего символа. При этом сдвиговый регистр загружается сразу;

• новый символ записывается в UDR до того, как выдвинут стоповый бит для предыдущего символа. При этом сдвиговый регистр записывается сразу после того, как будет выдвинут стоповый бит предыдущего символа.

При этом в регистре состояния UART — USR устанавливается бит UDRE — признак очистки регистра данных. Когда этот бит установлен, UART готов к приему следующего символа. При перезаписи UDR в 10(11) — разрядный сдвиговый регистр бит 0 сдвигового регистра обнуляется (стартовый бит), а бит 9 или 10 устанавливается (столовый бит). Если выбрано 9-битовое слово данных (установлен бит CHR9 в регистре UCR), бит ТХВ8 из UCR переписывается в 9-й бит сдвигового регистра передатчика.

После тактового импульса, следующего с частотой передачи, стартовый бит выдвигается на вывод TXD. Затем выдвигаются данные, начиная с младшего бита. После того как выдвинут стоповый бит, в сдвиговый регистр загружаются новые данные, если они были записаны в UDR во время передачи. При загрузке устанавливается бит UDRE. Если до выдвижения стопового бита в регистр UDR не поступают новые данные, UDRE остается установленным до последующей записи UDR. Если новые данные не поступили и на выводе TXD появляется стоповый бит, в регистре USR устанавливается флаг окончания передачи — ТХС.

Установка бита TXEN в UCR разрешает работу передатчика. При очистке бита TXEN вывод PD1 можно использовать для ввода/вывода данных. Если бит TXEN установлен, передатчик UART подключен к выводу PD1 независимо от установки бита DDD1 в регистре DDRD.

Прием данных

Структурная схема узла приема данных UART показана на рис. 2.40.

Рис. 2.40. Структурная схема узла приема данных UART

Логическая схема приемника обрабатывает сигнал на выводе RxD с частотой в 16 раз больше скорости передачи (для обработки одного бита принимаемой последовательности производится 16 выборок входного сигнала). В состоянии ожидания одна выборка логического нуля интерпретируется как спадающий фронт стартового бита, после чего запускается последовательность обнаружения стартового бита. Если в первой выборке сигнала обнаружен нулевой отсчет, приемник обрабатывает 8, 9 и 10 выборки сигнала на выводе RXD. Если хотя бы две и? трех выборок равны логической единице, стартовый бит считается шумом и приемник ждет следующего перехода из 1 в 0.

Если обнаружен стартовый бит, начинается обработка битов данных. Решение об уровне данных также производится по 8, 9 и 10 выборкам входного сигнала, уровень входного сигнала определяется по равенству двух выборок. После того как уровень данных определен, данные вдвигаются в сдвиговый регистр приемника.

Для определения стопового бита хотя бы две из трех выборок входного сигнала должны быть равны 1. Если это условие не выполняется, в регистре USR устанавливается флаг ошибки кадра FE. Перед чтением данных из регистра UDR пользователь должен проверять бит FE для обнаружения ошибок кадра.

Независимо от принятия правильного стопового бита по окончании приема символа принятые данные переписываются в UDR и устанавливается флаг RXC в регистре USR. Физически регистр UDR состоит из двух отдельных регистров, один используется для передачи данных, другой — для приема. При чтении UDR происходит доступ к регистру приемника, при записи — к регистру передатчика. При обмене 9-битовыми данными 9-й бит принятых данных записывается в бит RXB8 регистра UCR.

Если при приеме символа из регистра UDR не был прочитан предыдущий символ, в регистре UCR устанавливается флаг переполнения — OR. Установка этого бита означает, что последний принятый байт данных не переписывается из сдвигового регистра в регистр UDR и будет потерян. Бит OR буферирован и обновляется при чтении правильных данных из UDR. Таким образом, пользователь всегда может проверить состояние OR после чтения UDR и обнаружить происшедшее переполнение.

При сбросе бита RXEN в регистре UCR прием данных запрещается. При этом вывод PD0 можно использовать для ввода/вывода общего назначения. При установке RXEN приемник подключен к выводу PD0 независимо от состояния бита DDD0 в регистре DDRD.

Управление UART

Рис. 2.41. Регистр ввода/вывода UART (UDR)

Рис. 2.42. Регистр состояния UART (USR)

Регистр USR доступен только для чтения, в нем хранится информация о состоянии UART.

Бит 7 — RXC — прием завершен. Этот бит устанавливается в 1, когда принятый символ переписывается из сдвигового регистра приемника в регистр UDR. Бит устанавливается независимо от обнаружения ошибки кадра. Если установлен бит RXCIE в регистре UCR, при установке бита выполняется прерывание по завершении приема символа. RXC сбрасывается при чтении UDR. При использовании приема данных по прерыванию обработчик прерывания должен читать регистр UDR для сброса RXC, иначе при выходе из прерывания оно будет вызвано снова.

Бит 6 — ТХС — передача завершена. Этот бит устанавливается в 1, если символ из сдвигового регистра передатчика (включая стоповый бит) передан, а в регистр UDR не были записаны новые данные. Этот флаг особенно полезен при полудуплексной связи, когда передающее устройство должно перейти в режим приема и освободить линию связи сразу по окончании передачи. Если установлен бит TXIE в регистре UCR, при установке ТХС выполняется прерывания по окончании передачи. ТХС сбрасывается аппаратно при выполнении соответствующего вектора прерывания. Кроме того, бит можно сбросить, записав в него 1.

Бит 5 — UDRE — регистр данных UART пуст. Этот бит устанавливается в 1, когда данные, записанные в UDR, переписываются в регистр сдвига передатчика. Установка этого бита означает, что передатчик готов принять следующий символ для передачи. Если установлен бит UDRIE в регистре UCR, при установке этого бита выполняется прерывание окончания передачи. Бит UDRE сбрасывается при записи регистра UDR. При использовании передачи, управляемой прерыванием, подпрограмма обслуживания прерывания должна записывать UDR, чтобы сбросить бит UDRE, иначе при выходе из прерывания оно будет вызвано снова. При сбросе этот бит устанавливается в 1, чтобы показать готовность передатчика.

Бит 4 — FE — ошибка кадра. Этот бит устанавливается при обнаружении условия ошибки кадра, т. е. если стоповый бит принятого байта равен 0. Бит FE сбрасывается при приеме единичного стопового бита.

Бит 3 — OR — переполнение. Этот бит устанавливается при обнаружении условия переполнения, т. е. в том случае, когда символ из регистра UDR не был прочитан до того, как заполнился сдвиговый регистр приемника. Этот бит буферирован, т. е. остается установленным до тех пор, пока из регистра UDR не будут прочитаны правильные данные. Бит OR сбрасывается, когда принятые данные переписываются в UDR.

Биты 2…0 — в AT90S2313 зарезервированы и всегда читаются как 0.

Рис. 2.43. Регистр управления UART (UCR)

Бит 7 — RXCIE — разрешение прерывания по окончании приема. Если RXCIE = 1, установка бита RXC в регистре USR приводит к выполнению прерывания по окончании приема (при условии, что прерывания разрешены).

Бит 6 — TXCIE — разрешение прерывания по окончании передачи. Если этот бит установлен, установка бита ТХС в USR приводит к выполнению прерывания по окончании передачи (при условии, что прерывания разрешены).

Бит 5 — UDRIE — прерывание по очистке регистра данных последовательного порта. Если этот бит установлен, установка бита UDRE в USR приводит к выполнению прерывания по очистке регистра данных UART (при условии, что прерывания разрешены).

Бит 4 — RXEN — разрешение приемника. При установке этого бита разрешается работа приемника UART. Если приемник выключен, флаги ТХС, OR и FE не устанавливаются. Если эти флаги установлены, сброс RXEN не очищает их.

Бит 3 — TXEIS — разрешение передатчика. При установке этого бита разрешается работа передатчика UART. При запрещении работы передатчика во время передачи символа он продолжает работать, пока не будет очищен сдвиговый регистр и не будет передан символ, помещенный в UDR.

Бит 2 — CHR9 — 9-битовые посылки. Если этот бит установлен, принимаемые и передаваемые символы имеют длину 9 битов. Для передачи и приема 9-го символа используются биты RXB8 и ТХВ8 соответственно. 9-й бит можно использовать как дополнительный стоповый бит или как признак четности.

Бит 1 — RXB8 — 8 битов принимаемых данных. Если установлен бит CHR9, сюда записываегся 9-й бит принятых данных.

Бит 0 — ТХВ8 — 8 битов передаваемых данных. Если установлен биг CHR9, отсюда берется 9-й бит передаваемых данных.

Генератор скорости передачи

Генератор скорости передачи — это делитель частоты, который генерирует скорости в соответствии с нижеприведенным выражением:

BAUD = Fck/(16*(UBRR + 1)).

Здесь: BAUD — скорость передачи (бод); Fck — частота тактового генератора процессора; UBRR — содержимое регистра скорости передачи UART.

В следующей таблице приведены значения регистра UBRR и процентное отклонение от стандартной скорости передачи для стандартных частот кварцевых генераторов.

Рис. 2.44. Регистр скорости передачи (UBRR)

Это 8-разрядный регистр, который задает скорость передачи последовательного порта в соответствии с выражением, приведенным выше.

Более 800 000 книг и аудиокниг! 📚

Получи 2 месяца Литрес Подписки в подарок и наслаждайся неограниченным чтением

ПОЛУЧИТЬ ПОДАРОК