2.2. Обзор архитектуры AT90S2313

Файл регистров общего назначения

Регистровый файл микроконтроллера содержит 32 8-разрядных регистра общего назначения, доступ к которым осуществляется за один машинный цикл. Благодаря этому микроконтроллер может выполнить большинство команд за один цикл тактовой частоты.

АЛУ поддерживает арифметические и логические операции с регистрами, с константами и регистрами.

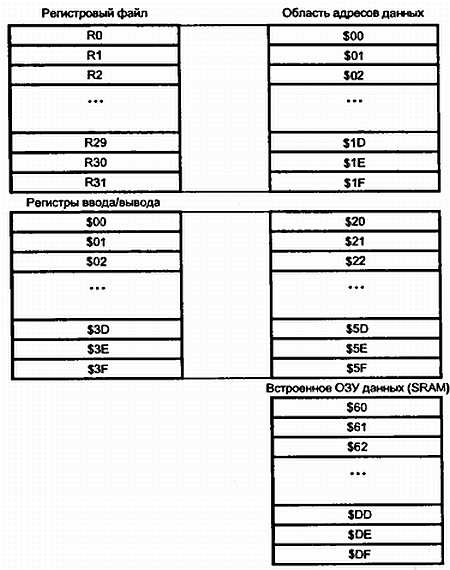

Кроме регистровых операций, для работы с регистровым файлом могут использоваться доступные режимы адресации, так как регистровый файл занимает адреса $00-$1F в области данных, обращаться к ним можно и как к ячейкам памяти.

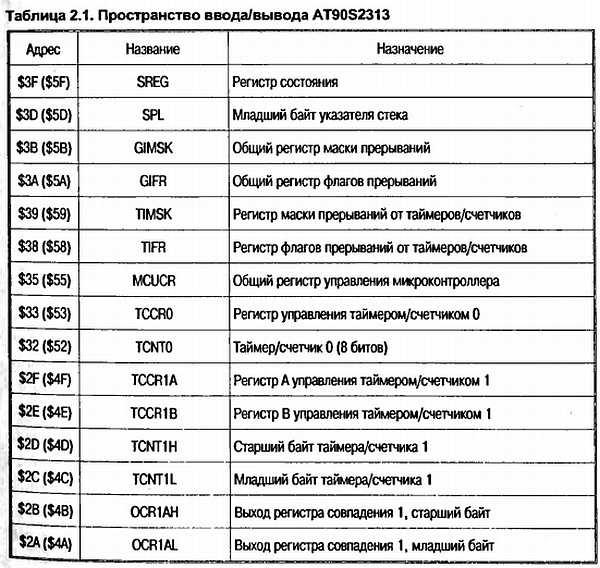

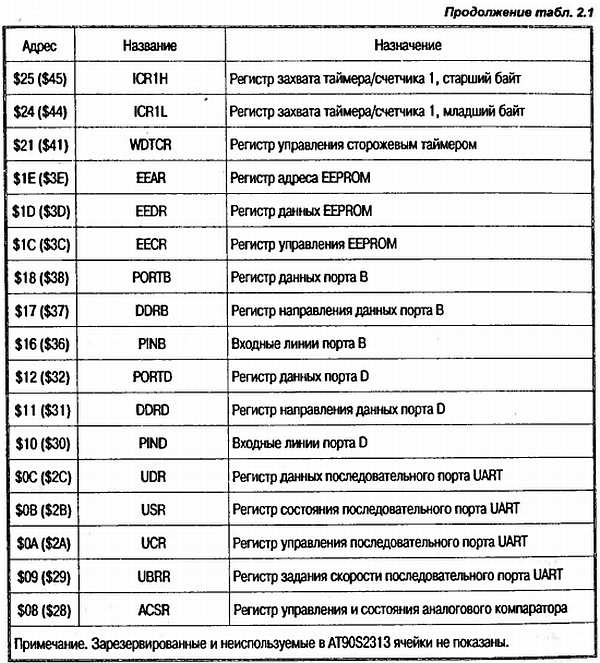

Пространство ввода/вывода состоит из 64 адресов для периферийных функций процессора, таких, как управляющие регистры, таймеры/счетчики и др. Доступ к пространству ввода/вывода может осуществляться непосредственно как к ячейкам памяти, расположенным после регистрового файла ($20—$5F).

Большинство команд, использующих регистры, могут использовать любые регистры общего назначения. Исключение составляют пять команд, оперирующих с константами: SBCI, SUBI, CPI, ANDI, ORI и команда LDI, загружающая регистр константой. Эти команды работают только со второй половиной регистрового файла — R16…R31.

Каждому регистру присвоен адрес в пространстве данных, они отображаются на первые 32 ячейки ОЗУ. Хотя регистровый файл физически размещен вне ОЗУ, подобная организация памяти дает гибкий доступ к регистрам.

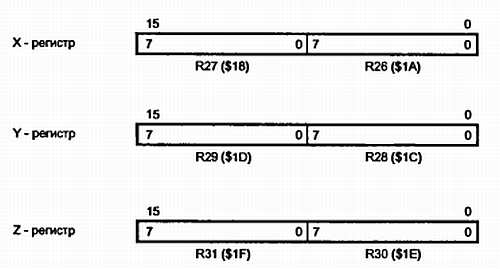

Шесть из 32 регистров — R26…R31 — можно использовать как три 16-разрядных адресных указателя в адресном пространстве данных. Один из трех адресных указателей (регистр Z) можно использовать для адресации таблиц в памяти программ. Эти регистры обозначаются как X, Y, Z и определены следующим образом:

Рис. 2.4. Регистры X, Y, Z

При различных режимах адресации эти регистры могут использоваться как фиксированный адрес, для адресации с автоинкрементом или с автодекрементом.

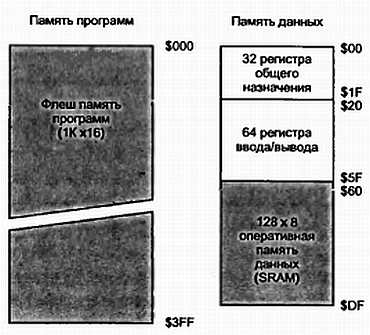

При разработке микроконтроллеров семейства AVR была использована так называемая гарвардская архитектура. Смысл ее состоит в том, что память программ и данных программы располагается в разных областях памяти. На рис. 2.5 изображена структура памяти микроконтроллеров AVR.

Доступ к памяти программ осуществляется следующим образом: во время выполнения одной команды следующая команда выбирается из памяти программ. Это дает возможность выполнять по одной команде за каждый машинный цикл.

При помощи команд относительных переходов и вызова подпрограмм осуществляется доступ ко всему адресному пространству. Большая часть команд микроконтроллеров AVR имеет размер 16-разрядов одно слово. Каждый адрес в памяти программ содержит одну 16- или 32-разрядную команду.

При обработке прерываний и вызове подпрограмм адрес возврата запоминается в стеке. Стек размещается в оперативной памяти данных общего назначения (SRAM), его размер ограничен только размером доступной памяти SRAM и ее использованием в программе. Все программы пользователя должны инициализировать указатель стека (SP) сразу после запуска микроконтроллера, до того как вызываются подпрограммы и разрешаются прерывания. Исключение составляют микроконтроллеры, не имеющие оперативной памяти данных (SRAM), например, AT90S1200. У этих микроконтроллеров реализован аппаратный стек глубиной 3. Это обязательно следует учитывать при написании для них программ.

Рис. 2.5. Структура памяти микроконтроллеров AVR

Все пространство памяти AVR является линейным и непрерывным.

Модуль прерываний имеет собственный управляющий регистр в пространстве ввода/вывода, и флаг глобального разрешения прерываний в регистре состояния. Каждому прерыванию назначен свой вектор в начальной области памяти программ. Различные прерывания имеют приоритет в соответствии с расположением их векторов. По младшим адресам расположены векторы с большим приоритетом.

Режимы адресации

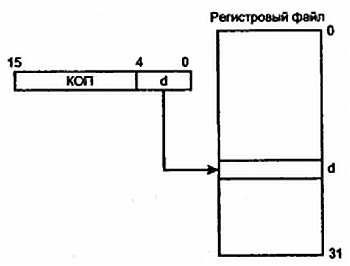

Прямая регистровая адресация с одним регистром Rd

Данные, над которыми осуществляется операция (или используются при выполнении операции), находятся в регистре d (Rd).

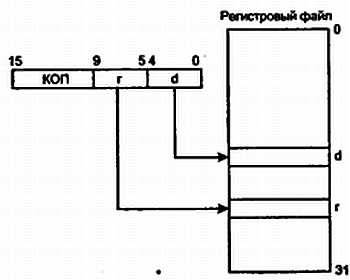

Прямая регистровая адресация с двумя регистрами — Rd и Rr

Данные, над которыми осуществляется операция, находятся в регистрах r(Rr) и d(Rd). Результат операции сохраняется в регистре d (Rd).

Рис. 2.6. Прямая регистровая адресация с одним регистром

Рис. 2.7. Прямая регистровая адресация с двумя регистрами

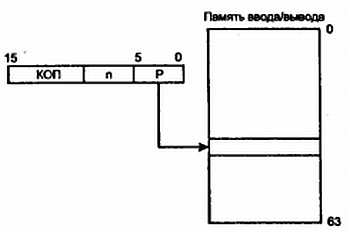

Прямая адресация к области ввода/вывода

Рис. 2.8. Прямая адресация к области ввода/вывода

n — адрес регистра, используемого в операции, находится непосредственно в коде команды, в битах 0…5.

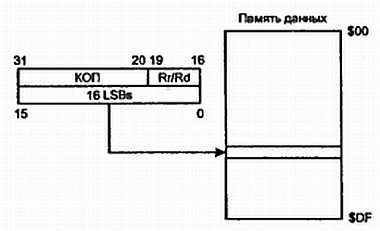

Прямая адресация к памяти данных

Рис. 2.9. Прямая адресация к памяти данных

16-разрядный адрес ячейки памяти данных находится в коде команды, состоящей из двух слов. Rr/Rd определяет регистр, используемый при работе с памятью данных (т. е. регистр, куда записываются результаты операции либо откуда они берутся для выполнения операции).

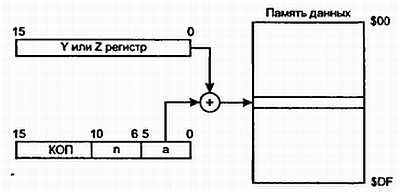

Косвенная адресация к памяти данных со смещением

Рис. 2.10. Косвенная адресация к памяти данных со смещением

Адрес операнда определяется как сумма содержимого Z или Y регистра и бит 0…5 кода команды.

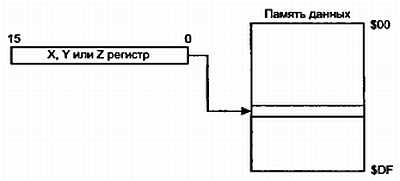

Косвенная адресация к памяти данных

Рис. 2.11. Косвенная адресация к памяти данных Адрес операнда находится в Х-, Y- или Z-регистре.

Косвенная адресация к памяти данных с предварительным декрементом

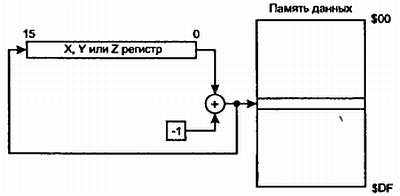

Рис. 2.12. Косвенная адресация к памяти данных с предварительным декрементом

Адрес операнда находится в Х-, Y- или Z-регистре. Однако перед выполнением операции соответствующий индексный регистр Х-, Y- или Z уменьшается на единицу.

Косвенная адресация к памяти данных с постинкрементом

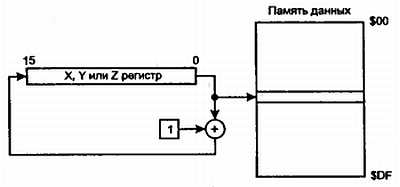

Рис. 2.13. Косвенная адресация к памяти данных с постинкрементом

Адрес операнда находится в Х-, Y- или Z-регистре. После выполнения операции соответствующий индексный регистр Х-, Y- или Z увеличивается на единицу.

Адресация к константам в памяти программ

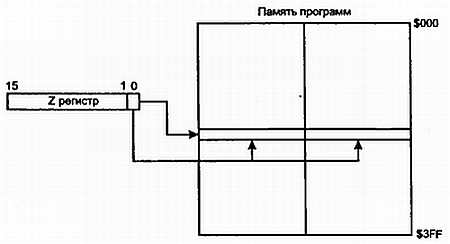

Рис. 2.14. Адресация к константам в памяти программ

Адрес константы — байта содержится в регистре Z. 15 старших битов определяют адрес слова, а младший (0) бит — младший или старший байт константы в памяти программ. Если в младшем бите

Косвенная адресация памяти программ

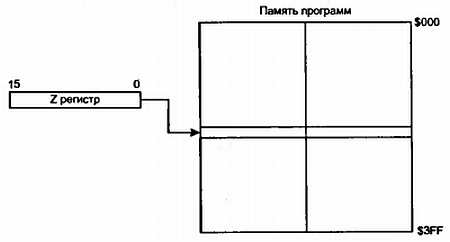

Рис. 2.15. Косвенная адресация памяти программ

После операций IJMP или ICALL выполнение программы продолжается с адреса, записанного в Z-регистре (т. е. в PC счетчик команд микроконтроллера записывается содержимое Z-регистра).

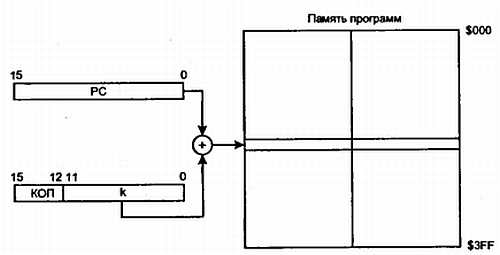

Относительная адресация памяти программ

Рис. 2.16. Относительная адресация памяти программ

После операций RJMP или RCALL выполнение программы продолжается с адреса РС+k+1. Относительный адрес к может составлять от -2048 до 2047.

Арифметико-логическое устройство

Арифметико-логическое устройство (АЛУ) микроконтроллера непосредственно подключено к 32 регистрам общего назначения. За один машинный цикл АЛУ производит операции между регистрами регистрового файла. АЛУ может выполнять арифметические, логические и битовые операции.

Память программ

AT90S2313 содержит 2 Кб флэш-памяти для хранения программ. Флэш-память организована как 1Кх16. В фирменном описании микроконтроллера утверждается, что флэш-память можно перепрограммировать до 1000 раз.

Программный счетчик имеет ширину 10 битов и позволяет адресовать 1024 слов памяти программ.

Способы занесения информации (т. е. программ) во флэш-память микроконтроллера будут рассмотрены дальше.

EEPROM память данных

AT90S2313 содержит 128 байтов электрически стираемой энергонезависимой памяти (EEPROM). EEPROM организована как отдельная область данных, каждый байт которой может быть прочитан и при необходимости перезаписан. EEPROM выдерживает не менее 100 000 циклов записи/стирания. К этой памяти может обращаться программа, считывая или записывая какие-либо данные. Кроме того, данные в эту память можно занести с помощью специального устройства — программатора, на этапе изготовления и программирования конструкции. Ее удобно использовать для хранения каких-либо констант.

Оперативная память данных

На рис. 2.17 показана организация памяти данных в AT90S2313.

224 ячейки памяти включают в себя регистровый файл, память ввода/вывода и оперативную память данных.

Рис. 2.17. Организация памяти данных в микроконтроллере AT90S2313

Первые 96 адресов используются для регистрового файла и памяти ввода/вывода, следующие 128 — для ОЗУ данных.

При обращении к памяти используются пять различных режимов адресации: прямой, непосредственный со смещением, непосредственный, непосредственный с предварительным декрементом и непосредственный с постинкрементом. Регистры R26…R31 регистрового файла используются как указатели для непосредственной адресации.

Прямая адресация имеет доступ ко всей памяти данных. Непосредственная адресация со смещением используется для доступа к 63 ячейкам, базовый адрес которых задается содержимым регистров Y или Z.

Для непосредственной адресации с инкрементом и декрементом адреса используются адресные регистры X, Y и Z.

При помощи любого из этих режимов можно осуществлять доступ ко всем 32 регистрам общего назначения, 64 регистрам ввода/вывода и 128 ячейкам ОЗУ.

Время выполнения команд

ЦПУ процессора AVR управляется тактовой частотой, генерируемой внешним резонатором. Внутреннее деление частоты генератора в микроконтроллерах семейства AVR не используется.

В микроконтроллере процесс выполнения команд организован так, что при выборе команды из памяти программ происходит выполнение предыдущей команды. Это позволяет достичь быстродействия 1 MIPS на МГц.

Все устройства ввода/вывода и периферийные устройства AT90S2313 располагаются в пространстве ввода/вывода. Различные ячейки этого пространства доступны через команды IN и OUT, пересылающие данные между одним из 32 регистров общего назначения и пространством ввода/вывода. К регистрам $00…$1F можно осуществлять побитовый доступ командами SBI и CBI. Значение отдельного бита этих регистров можно проверить командами SBIC и SBIS. Дополнительную информацию по этому вопросу можно найти в описании системы команд.

При использовании специальных команд IN, OUT, SBIS и SBIC должны использоваться адреса $00…$3F. При доступе к регистру ввода/вывода как к ячейке ОЗУ к его адресу необходимо добавить $20. В приведенной выше таблице адреса регистров в памяти данных приведены в скобках.

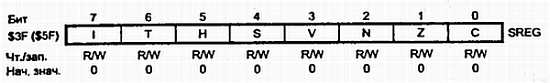

Регистр состояния — SREG

Рис. 2.18. Регистр состояния

Регистр состояния расположен по адресу $3F ($5F) пространства ввода/вывода и определен следующим образом:

Бит 7 — I: общее разрешение прерываний. Для разрешения прерываний этот бит должен быть установлен в единицу. Управление отдельными прерываниями производится регистрами маски прерываний — GIMCK и TIMCK. Если бит 1 = 0, независимо от состояния GIMCK/TIMCK прерывания запрещены. Бит I обнуляется аппаратно после входа в прерывание и восстанавливается в состояние 1 командой возврата из подпрограммы обработки прерываний RETI, для разрешения обработки последующих прерываний.

Бит 6 — Т: хранение копируемого бита. Бит из регистра регистрового файла может быть скопирован в Т командой BST, бит Т может быть скопирован в бит регистрового файла командой BLD.

Бит 5 — Н: флаг половинного переноса. Этот флаг индицирует перенос из младшей половины байта при некоторых арифметических операциях. Подробнее об этом можно прочитать в описании системы команд.

Бит 4 — S: бит знака, S = N XOR V. Бит S равен исключающему ИЛИ между флагами N (отрицательный результат) и V (переполнение дополнения до двух). Если после операций сложения или вычитания чисел со знаком флаг переполнения V будет установлен в 1, то результатом будет 9-разрядное число, причем старшим (т. е. знаковым) разрядом числа будет флаг S, а 8 остальных битов результата будут храниться в 8-разрядном регистре-приемнике выполнявшейся операции.

Бит 3 — V: флаг переполнения дополнения до двух. Этот флаг надо проверять после операций сложения или вычитания чисел в дополнительном коде. Он устанавливается в том случае, если результат операции выходит за пределы диапазона от -128 до +127. Это — допустимый диапазон чисел со знаком, которые можно сохранить в 8 разрядах. Соответственно, бит V установится в 1, если при сложении двух положительных чисел получится число, большее 127, или при сложении двух отрицательных чисел — меньше -128.

Бит 2 — N: флаг отрицательного результата. Этот флаг устанавливается в 1, если старший (знаковый) разряд (бит 7) равен 1, что означает, что результат отрицателен. Следует, однако, отметить, что флаг может быть также установлен и в результате логических операций.

Бит 1 — Z: флаг нулевого результата. Этот флаг индицирует нулевой результат различных арифметических и логических операций. Подробнее об этом можно прочитать в описании системы команд.

Бит 0 — С: флаг переноса. Этот флаг индицирует перенос в арифметических и логических операциях. Подробнее об этом можно прочитать в описании системы команд.

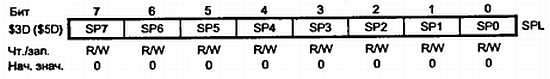

Указатель стека SP

Этот 8-разрядный регистр с адресом $3D ($5D) хранит указатель стека процессора AT90S2313. Восьми разрядов достаточно для адресации ОЗУ в пределах $60 — $DF.

Рис. 2.19. Указатель стека

Указатель стека указывает на область памяти, в которой сохраняется адрес возврата из подпрограмм и прерываний. Также с помощью стека подпрограммы могут получать или передавать данные.

Область стека в ОЗУ должна быть задана до того, как произойдет любой вызов подпрограммы или будут разрешены прерывания. Указатель стека уменьшается на 1 при записи данных в стек командой PUSH, и уменьшается на 2 при вызове подпрограммы командой CALL или обработке прерывания. Указатель стека увеличивается на 1 при выборе данных из стека командой POP и увеличивается на 2 при выполнении команд возврата из подпрограммы или обработчика прерывания (RET или RETI).

Более 800 000 книг и аудиокниг! 📚

Получи 2 месяца Литрес Подписки в подарок и наслаждайся неограниченным чтением

ПОЛУЧИТЬ ПОДАРОК