Что такое транзисторно-транзисторные логические схемы?

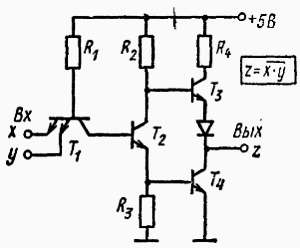

На рис. 12.12 представлен пример построения схемы ТТЛ, выполняющей функции И — НЕ. Это решение соответствует интегральной схеме типа UCY7400 и 134ЛБ1, содержащей четыре вентиля.

Рис. 12.12. Логическая ТТЛ-схема, выполняющая функции И — НЕ на интегральных микросхемах типа UCY7400 или 134ЛБ

Схема работает следующим образом. Транзистор Т1 с двумя эмиттерами осуществляет логическое произведение (элемент И), а остальные транзисторы образуют выходной противотактный усилитель, осуществляющий функцию отрицания (элемент НЕ). Если хотя бы на одном из входов имеется сигнал логического 0 (ниже + 0,4 В), то транзистор Т1 находится в состоянии насыщения, а транзистор Т2 — в состоянии запирания. В этом случае резистор R3 соединяет базу транзистора Т1 с массой, что вызывает его запирание.

Транзистор Т3 в этих условиях работает как эмиттерный повторитель, поскольку нагрузочное сопротивление схемы и сопротивление транзистоpa T4 в состоянии запирания значительно больше, чем сопротивление R4. Выходной сигнал повторителя соответствует 1 (более +2,4 В).

При подаче сигнала, соответствующего 1, на оба входа вентиля эмиттерные переходы входного транзистора Т1 будут смещены в обратном направлении и ток базы этого транзистора будет протекать через коллекторный переход транзистора Т2, который находится в состоянии насыщения. В режим насыщения перейдет также транзистор T4 и запрется транзистор Т3. На выходе будет сигнал 0.

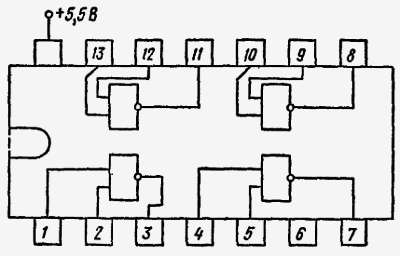

Соединения в корпусе интегральной микросхемы UCY7400 показаны на рис. 12.13.

Техника ТТЛ-схем отличается высоким быстродействием, простотой реализации, малым потреблением мощности и большой нагрузочной способностью. Благодаря этим достоинствам схемы ТТЛ являются наиболее распространенными логическими схемами.

Рис. 12.13. Соединения в интегральной микросхеме типа UCY7400

Более 800 000 книг и аудиокниг! 📚

Получи 2 месяца Литрес Подписки в подарок и наслаждайся неограниченным чтением

ПОЛУЧИТЬ ПОДАРОК