Некторые типовые цифровые схемы

Благодаря усилиям полупроводниковой промышленности цифровые схемы удивительно легки и приятны. Почти нет случаев, когда приходится класть цифровую схему на «хлебную доску», как это часто происходит с линейными схемами. Вообще говоря, единственными серьезными проблемами являются синхронизация и шумы.

Мы в последующем расскажем об этом. Здесь уместно проиллюстрировать синхронизацию на нескольких примерах последовательностных схем. Некоторые из этих функций могут быть выполнены с помощью БИС, однако рассматриваемые реализации сделаны на хорошем уровне и позволяют проиллюстрировать, какого типа схемы можно строить с помощью имеющихся средств.

8.29. Счетчик по модулю n

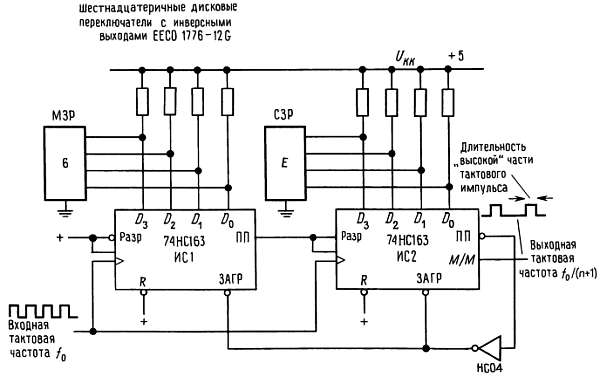

Изображенная на рис. 8.88 схема на каждые n входных тактовых импульсов вырабатывает один выходной импульс. Значение n есть 8-разрядное число, которое вы задаете с помощью двух барабанных шестнадцатеричных переключателей. Схемы `163 являются 4-разрядными синхронными суммирующими счетчиками с синхронной загрузкой (когда вход LD'- низкий) через D-входы. Идея состоит в загрузке дополнительного кода, счете вверх до FFn и перезагрузке по следующему тактовому импульсу. Поскольку мы сформировали значение перезагрузки с помощью источника +5 (с общим заземленным выводом переключателя), то эти уровни являются отрицательно-истинными для отображения набора переключателей, это означает, что загружаемые значения интерпретируются как истинные положительные, равные дополнительному до 1 значению, установленному на переключателях.

Рис. 8.88. Счетчик по модулю n.

Упражнение 8.35. Путем вычисления истинного положительного значения, которое будет установлено на переключателях рис. 8.88, докажите истинность последнего утверждения.

Работа схемы совершенно очевидна. Для каскадирования синхронных счетчиков вы соединяете все тактовые входы вместе, затем соединяете выход «максимальный счет» каждого счетчика с разрешением следующего счетчика. Для схемы `163 выход RCO (ripple-clock output — выход переполнения ПП) выставляет ВЫСОКИЙ уровень при максимальном счете, разрешая второму счетчику посредством установления разрешения (ВЫСОКОГО уровня) на входах ENT и ENP (Разр). Таким образом, ИС1 повышает свое значение на каждый тактовый импульс, а ИС2 повышает свой счет на каждый тактовый импульс после того, как ИС1 насчитает значение Fn. Таким образом, два счетчика считают пока не достигнут состояния FFn, в этой точке входы загрузки LD' устанавливаются в истинное значение. Это приводит к синхронной предзагрузке на следующем такте. Здесь мы выбрали счетчики с синхронной загрузкой для того, чтобы избежать логических состязаний (и короткого импульса RCO), которые могут возникнуть в счетчике с асинхронной загрузкой. К сожалению, счетчик при этом делит на n + 1, а не на n.

Упражнение 8.36. Объясните, что произойдет, если счетчик с асинхронной загрузкой (например, `191) заменить на счетчик с синхронной загрузкой `163. Покажите, в частности, как могут образовываться короткие импульсы. Покажите также, что предыдущая схема делит на n + 1, в то время как при асинхронной загрузке будет осуществляться деление на n (если схема вообще будет работать).

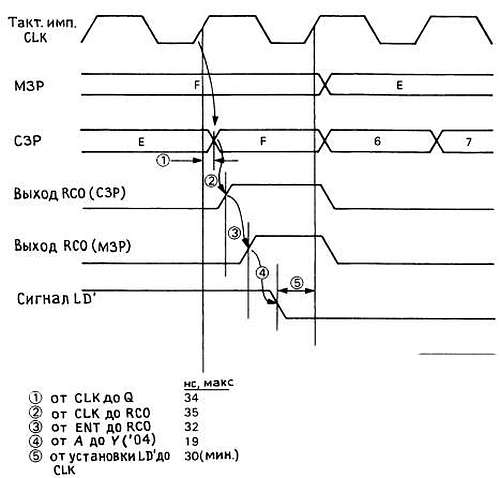

Временная диаграмма. До какой максимальной частоты может считать наш счетчик? Схема 74НС163 имеет гарантированную максимальную частоту счета fмакс 27 МГц. Однако в нашей схеме существуют дополнительные временные задержки, связанные с каскадным соединением (ИС2 должна «узнавать», что ИС1 уже достигла максимального счета за время до следующего тактового импульса), и с соединением «загрузка при переполнении». Для изображения максимальной частоты, при которой гарантируется работа схемы, мы должны добавить задержку для наихудшего случая и быть уверенным, что остается достаточно времени да переустановку. Посмотрите на рис. 8.89, где мы изобразили временную диаграмму, показывающую последовательность загрузки, которая выполняется при максимальном счете.

Рис. 8.89. Временная диаграмма счетчика по модулю n и расчет максимальной скорости работы.

Изменение сигнала с НИЗКОГО на ВЫСОКИЙ уровень на каком-либо выходе Q следует за положительным фронтом тактового сигнала максимум через 34 нc. Это интересно (но не относится к делу), что загружаемая последовательность использует выход RCO (переноса); сигнал RCO следует за положительным фронтом тактового импульса, что при максимальной частоте счета составляет максимум 35 нc. Сигнал переноса RCO ИС2 появляется после наличия входного разрешения (при условии, конечно, что это происходит при максимальном счете) максимум через 32 нc. Схема 74НС04 добавляет задержку максимум в 19 нc для генерации сигнала ЗАГРУЗКА' (LD'), которая должна предшествовать сигналу такта (isetup) как минимум на 30 нc. Что приводит нас к следующему тактовому импульсу; таким образом 1/fмакс = (35 + 32 + 19 + 30) нc, или fмакс = 8,6 МГц. Что значительно меньше, чем максимально гарантируемая частота счета одного 74НС163.

Упражнение 8.37. Покажите, проведя подобное вычисление, что два синхронных каскадно соединенных счетчика 74НС163 (без загрузки при переполнении) имеют максимальную частоту счета 15,4 МГц.

Конечно, если вам необходима более высокая скорость, вы можете использовать более быструю логику. Проделав те же самые вычисления для логики 74F (для которой максимальная частота счета одного счетчика 74F163 составляет 100 МГц), мы находим fмакс = 29 МГц. Нужно отметить устройство `НС40103 при рассмотрении счетчиков по модулю n, которое представляет собой 8-разрядный синхронный вычитающий счетчик с параллельной загрузкой (синхронной или асинхронной), с дешифрацией нулевого состояния и входом сброса в максимальное состояние. Этот счетчик имеет близкого родственника `НС40102, идентичного, за исключением его «организации», сдвоенному двоично-десятичному.

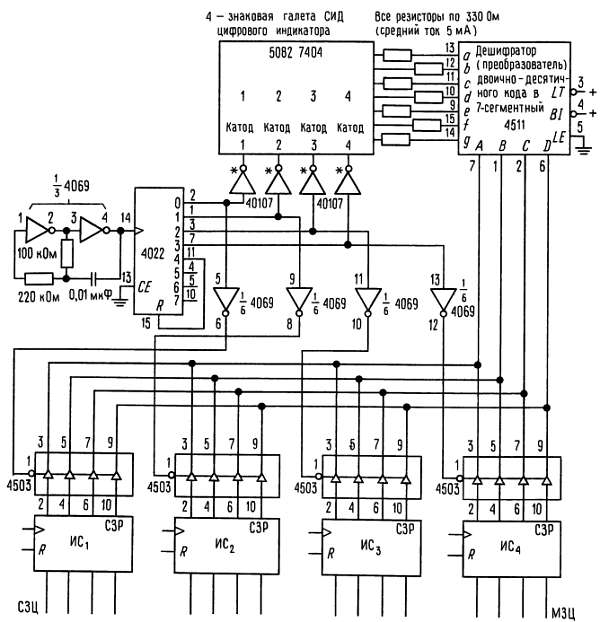

8.30. Мультиплексируемый цифровой индикатор на светодиодах

Этот пример иллюстрирует метод мультиплексного отображения, который заключается в том, что n цифр каждого числа последовательно и быстро воспроизводится на 7-сегментных светодиодных индикаторах. (Могут, конечно, использоваться не только цифровые символы, и конструкция индикаторов может отличаться от распространенной 7-сегментной организации). Коммутация индикаторов применяется для экономии и упрощения: непрерывное воспроизведение каждого знака требует установки для каждой цифры индивидуальных дешифраторов, формирователей и токоограничивающих резисторов, а также индивидуальных связей между каждым регистром и соответствующим дешифратором (4' линии) и между каждым формирователем и соответствующим индикатором (7 проводов); жуткая путаница!

В методе мультиплексирования требуется лишь один дешифратор/формирователь и один набор токоограничивающих резисторов. Кроме того, так как светодиодные цифровые индикаторы выпускаются в виде n-символьных галет, причем соответствующие сегменты всех символов объединены, количество взаимных соединений сокращается довольно существенно. Так, 8-знаковый индикатор требует 15 соединений при использовании этого метода (7 сегментных входов, общие для всех цифр, плюс один катод или анод в цепи возврата каждой цифры), при непрерывном же воспроизведении их потребуется 57. Еще одно любопытное преимущество этого метода состоит в том, что субъективно воспринимаемая глазом яркость будет в этом случае выше, чем при непрерывном свечении всех цифр при той же средней яркости.

На рис. 8.90 изображена принципиальная схема индикации.

Рис. 8.90. Коммутируемый цифровой индикатор для четырех знаков. Числа с внешней стороны графических обозначений соответствуют номерам контактов ИС.

Цифры, которые должны быть воспроизведены на индикаторе, хранятся в регистрах ИС1-ИС4. Вместо регистров можно использовать счетчики, если устройство представляет собой счетный частотомер или набор защелок (триггеров), получающих данные от компьютера или выхода АЦП и т. п. В этом случае при данном методе каждая цифра последовательно вводится на внутреннюю 4-разрядную шину (в рассматриваемом примере через КМОП-буферы с тремя состояниями 4503), дешифрируется и отображается на индикаторе (схема 4511 представляет дешифратор двоично-десятичного кода в 7-сегментный с формирователем сигналов управления цифровым индикатором).

В этой схеме два инвертора используются для получения классического КМОП генератора, работающего на частоте 1 кГц и подающего сигналы на 8-разрядный счетчик-дешифратор 4022. Каждый выход счетчика последовательно устанавливается в состояние ВЫСОКОГО уровня и выводит на шину очередную цифру.

Одновременно он запитывает катод соответствующего индикатора, подавая на него НИЗКИЙ уровень через мощный буфер с открытым коллектором 40107. Счетчик 4022 циклически проходит состояние от 0 до 3, а при достижении числа 4 каждый раз сбрасывается. Мультиплексируемая индикация может работать и при большем количестве цифр. Она повсюду используется в многоцифровых индикаторах на светодиодах. Попытайтесь посмотреть вокруг — перед вашими глазами море цифр и знаков.

Многие БИС, ориентированные на воспроизведение информации, как, например, счетчики, реле времени и часы, содержат встроенную схему коммутации индикатора и даже формирователи. Более того, существуют БИС управления индикацией (например, 74С922 и 74Ц912); они проделывают всю ту работу, которая раньше выполнялась с помощью ИМС средней степени интеграции.

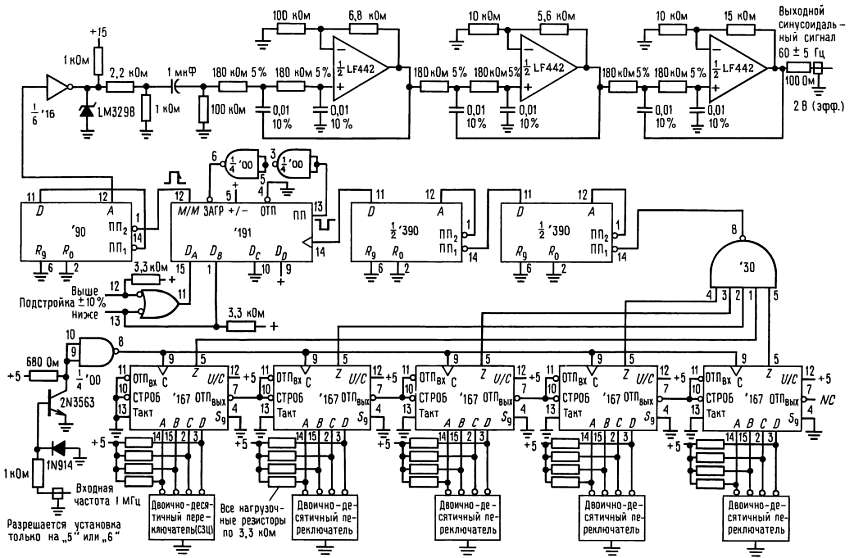

8.31. Привод звездного телескопа

Схема, изображенная на рис. 8.91, была спроектирована для управления приводом Гарвардского 62-дюймового оптического телескопа.

Рис. 8.91. Прецизионный формирователь сигнала переменного тока частотой 60 Гц. Выходная частота равна хх. ххх. Для задания звездной скорости ключи устанавливаются на значение 60 165.

Для питания экваториального привода двигателя (совершающего 1 оборот в день) требуется источник электроэнергии переменного тока, частота которого должна устанавливаться равной любому значению около 60 Гц (скажем, от 55 до 65 Гц). Эта частота не может точно равняться 60 Гц по следующим причинам: а) звезды и Солнце движутся с разной скоростью, поэтому потребуется частота порядка 60,1643 Гц; б) проходя наклонно через атмосферу, звездный свет претерпевает рефракцию; это преломление зависит от зенитного узла и, следовательно, видимое движение будет происходить с неравномерной скоростью; в) иногда может возникнуть желание взглянуть на Луну, планеты или кометы, которые движутся с неодинаковыми скоростями. Было решено использовать 5-значный дискретный умножитель частоты для получения выходных импульсов с частотой следования fвхn/105, где n — пятизначное десятичное число, которое устанавливается на передней панели с помощью двоично-десятичных барабанных переключателей.

Выходная частота умножителя будет порядка 600 кГц, поскольку входная частота fвх формируется стабильным кварцевым генератором и равна точно 1 МГц. На выходе умножителя частота делится на 104 посредством четырех декадных счетчиков, причем последний счетчик выполнен в виде делителя на 5, а после него установлен делитель на 2, служащий для получения симметричных импульсов с частотой 60 Гц. Для стабилизации амплитуды прямоугольной формы выходной сигнал поступает на ограничитель, выполненный на стабилитроне, а затем с помощью 6-звенного НЧ-фильтра Баттерворта с частотой среза f0, равной 90 Гц, преобразуется в хороший синусоидальный сигнал. (Можно считать, что фильтр «вычищает» из прямоугольного сигнала высшие гармонические составляющие, или «обертоны»). Далее, с помощью усилителя с «перекомпенсацией», рассмотренного в разд. 4.35, вырабатывается переменное напряжение 115 В.

Выходной сигнал фильтра на экране осциллографа выглядит идеальным, так как 6-звенный фильтр Баттерворта позволяет в данной схеме снизить наибольшую гармонику до 1,5 % от значения амплитуды нефильтрованного сигнала, что означает затухание более чем на 35 дБ. Заметим, что данный метод формирования синусоидальных колебаний удобен лишь тогда, когда частота входного сигнала ограничена узким диапазоном. Входы управления ±10 % позволяют изменять частоту выходного синусоидального сигнала на 10 % за счет того, что коэффициент деления третьего делителя устанавливается равным 9 или 11. Эта ступень представляет собой делитель по модулю n, изображенный на рис. 8.88.

8.32. Генератор последовательности из n импульсов

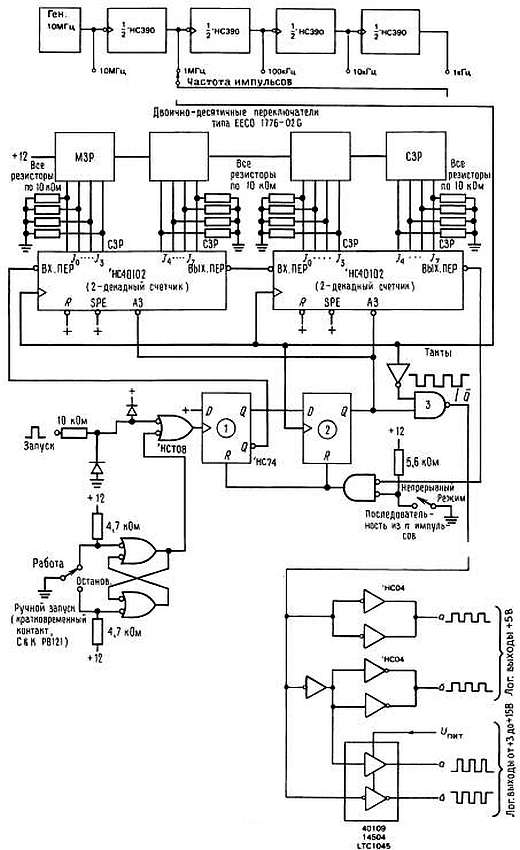

Генератор последовательности из n импульсов представляет собой широко используемый небольшой прибор для тестирования. По внешнему сигналу запуска (или используя ручной запуск) он вырабатывает на выходе пачку из n импульсов с заданной частотой следования, которая может иметь ряд дискретных значений. На рис. 8.92 показана принципиальная схема генератора.

Рис. 8.92. Генератор последовательности из n импульсов.

Интегральные схемы `НС40102 представляют собой КМОП высокоскоростные 2-декадные вычитающие счетчики, тактируемые непосредственно частотой, выбираемой десятичным делителем, подключенным к 10-МГц кварцевому генератору. Счетчики делителя могут блокироваться либо активным уровнем на выходе A3 (асинхронная загрузка), либо пассивным уровнем на входе переноса (Вх. пер.). Когда запускающий импульс появляется (заметим, что используется `НСТ-серия на входе для совместимости с биполярной ТТЛ), триггер-1 выдает разрешение счетчику, а триггер-2 обеспечивает синхронизацию счета после следующего положительного фронта тактового импульса. Тактовые импульсы проходят через вентиль И-НЕ-3 до тех пор, пока счетчики не достигнут нуля, в это время оба триггера сбрасываются в исходное состояние; осуществляется параллельная загрузка в счетчик числа n, задаваемого двоично-десятичными переключателями, запрещается счет и схема готова для другого запуска. Заметим, что использование резисторов, подключенных к общему проводу, в этой схеме означает, что должны быть использованы двоично-десятичные переключатели в прямом коде (предпочтительнее, чем в дополнительном). Отметим также, что вход ручного запуска должен иметь защиту от дребезга, так как он тактирует триггер. Защита от дребезга не требуется для переключателя режимов, который просто разрешает формирование на выходе непрерывной последовательности импульсов.

Выходной каскад обеспечивает две пары прямых и инвертированных сигналов. Запараллеленные инверторы `НС04 выдают обычный логический размах +5 В благодаря использованию технологии КМОП. Мы запараллелили инверторы для увеличения нагрузочной способности. Схема может обеспечивать по крайней мере ток нагрузки ±10 мА при логических уровнях, отличающихся на 0,3 В от границ напряжения питания. Если вам требуется больший выходной ток, вы можете заменить инверторы на схемы `АС04, запараллеленная пара которых будет давать выходной ток до +50 мА при таких же значениях логических уровней.

Мы добавим пару усилителей, изображенных в прямоугольнике, которые могут управлять логикой, способной работать при напряжении, отличном от +5 В: например, маломощные часто используемые при проектировании КМОП серии 4000В и 74С работают непосредственно от батарей +9 В (они нормально работают при напряжении от 3 до 15 В); НС-логические элементы работают при напряжении питания от 2 до 6 В. Было выдвинуто предложение, чтобы КМОП серия `АС оперировала при напряжении +3,3 В (JEDEC стандарт N08). Интегральные схемы 40109, 14504 и LTC1045 являются преобразователями уровней, это кристаллы с активным выходным каскадом, который запитывается от второго источника питания, который может быть выше или ниже напряжения +5 В. Таким образом, мы получаем чистые логические уровни КМОП-схем.

Более 800 000 книг и аудиокниг! 📚

Получи 2 месяца Литрес Подписки в подарок и наслаждайся неограниченным чтением

ПОЛУЧИТЬ ПОДАРОК