Последовательные функции, реалзуемые на стандартных ИМС

Различные сочетания триггеров и вентилей, так же как и рассмотренные ранее комбинационные схемы, могут быть размещены на одном кристалле ИМС. В последующих разделах мы дадим обзор наиболее часто используемых типов ИМС в соответствии с выполняемыми функциями. Так же, как и в случае с небогатой комбинационной логикой, программируемые логические устройства (ПМЛ и GAL, в частности) создают притягательную альтернативу для использования жестких последовательных функций. Мы также об этом будем говорить после рассмотрения стандартных функций.

8.24. Фиксирующие схемы-защелки и регистры

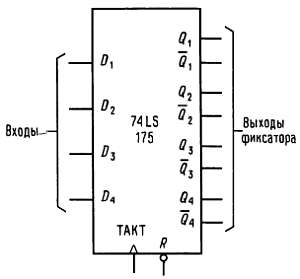

Фиксирующие схемы-защелки и регистры позволяют запоминать комбинацию двоичных разрядов, которая подана на их входы, и хранить ее после изменения входных сигналов. Регистр можно построить с помощью набора D-триггеров, но в этом случае число входов и выходов у него будет больше, чем требуется обычно. Так как в данном применении нет необходимости использовать раздельно тактовые и установочные входы, эти цепи можно объединить для всех триггеров; это позволит сократить число выводов ИМС и даст возможность разместить в стандартном 20-контактном корпусе 8 триггеров. Так, например, популярная схема `574 представляет собой 8-разрядный D-регистр с фиксацией по положительному фронту и с выходами на три состояния; схема `273 подобна ей, но имеет возможность сброса вместо выходов на 3 состояния. На рис. 8.69 представлен 4-разрядный D-регистр с прямым и инверсными выходами.

Рис. 8.69. 4-разрядный D-триггер типа 74LS175

Термин «фиксатор» или «защелка» обычно служит для обозначения специального типа регистров, которые в открытом состоянии отслеживают на своих выходах входные сигналы, а в закрытом хранят их последнее значение. Так как термин «фиксатор» стал неоднозначным, часто для того, чтобы отличить друг от друга два очень сходных устройства, используют термины «прозрачный фиксатор» (собственно «защелка») и «регистр D-типа». Например, схема `573 представляет собой 8-разрядный «прозрачный фиксатор», эквивалентный `574 D-регистру.

Существуют некоторые вариации фиксаторов/регистров, такие как: а) запоминающие устройства с произвольной выборкой (ЗУПВ), которые позволяют вам как записывать, так и читать массив регистров (обычно большой), но только по раздельности. ЗУПВ имеют размеры от нескольких байт до 1 Мбайт и более и обычно используются в системах памяти микропроцессорных устройств (см. гл. 10 и 11); б) адресуемые защелки, устройства многоразрядной фиксации, которые позволяют осуществлять доступ к отдельным битам, не изменяя содержимого остальных; в) защелка или регистр, встраиваемые в большой кристалл, например цифро-аналоговый преобразователь; такое устройство необходимо, когда входные данные существуют не все время (в течение тактирующего фронта), поскольку внутренний регистр может хранить данные.

В табл. 8.9 в конце главы представлены данные большинства полезных регистров и защелок. Отметим такие особенности этих устройств, как: вход разрешения, сброс, выход на 3 состояния и «противоположное» расположение выводов (входы на одной стороне корпуса, а выходы - на другой). Последнее очень важно, когда вы используете для размещения печатную плату.

8.25. Счетчики

Как мы уже видели ранее, соединяя триггеры друг с другом, можно построить счетчик. Существует поразительное множество разнообразных устройств такого типа, выполненных в одном корпусе. Попытаемся выяснить некоторые их характерные особенности.

Объем или размер счетчика. Вы можете найти в популярной 4-разрядной серии как двоично-десятичные, так и двоичные (или шестнадцатеричные, делители на 16). Существуют счетчики и на большее число разрядов — до 24 (но не все доступны), а также счетчики «по модулю n», позволяющие производить деление на целое число n, которое задается с помощью входного слова. Для получения большего числа разрядов счетчики, в том числе и синхронные, можно соединять каскадно.

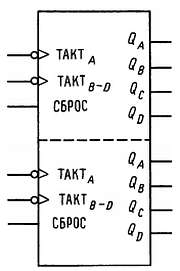

Тактирование. Среди выпускаемых промышленностью в виде стандартных ИМС счетчиков одни могут тактироваться положительным перепадом, а другие отрицательным. Более существенно, здесь то, является ли счетчик синхронным или асинхронным. В синхронных счетчиках тактирование всех триггеров происходит одновременно, а в асинхронных каждый последующий триггер тактируется выходом предыдущего. В асинхронных счетчиках имеют место переходные состояния, так как начальные триггерные ступени перебрасываются несколько раньше последующих: Например, при переходе от рис. 8.70.

Рис. 8.70. Сдвоенный двоично-десятичный счетчик со сквозным переносом типа 74LS390.

Сдвоенный двоично-десятичный счетчик со сквозным переносом типа 74LS390. числа 7 (0111) к числу 8 (1000) асинхронный счетчик пройдет через состояния 6, 4 и 0. Это может привести к ложной работе схемы, воспринимающей текущее состояние счетчика, если в ней не будут предусмотрены соответствующие меры. В таких случаях желательно использовать что-либо подобное D-триггеру, чтобы анализировать состояние счетчика только по тактовому перепаду. Асинхронные счетчики работают медленнее синхронных, так как они накапливают задержку распространения. Для облегчения наращивания (путем подключения выхода Q одного счетчика к тактовому входу последующего) асинхронные счетчики должны иметь вход, который работает по заднему фронту, синхронные счетчики тактируются положительным перепадом.

Мы рекомендуем семейство `160-`163 4-разрядных синхронных счетчиков для большинства применений, где не требуется специальных особенностей. Схемы 590 и 582 являются хорошими 8-разрядными синхронными счетчиками. На рис. 8.70 показан сдвоенный двоично-десятичный счетчик типа 390.

Суммирование/вычитание. Некоторые счетчики могут считать в обоих направлениях. Для этого существует две возможности: а) отдельный управляющий вход (+/—), который устанавливает направление счета и б) два раздельных счетных входа для прямого и обратного счета. Например, схемы `191 и `193 соответственно. Схемы `569 и `579 являются 8-разрядными счетчиками, считающими в обоих направлениях.

Предварительная установка и очистка. Большинство счетчиков имеют информационные входы, которые позволяют предварительно заносить в них заданное число. Это, в частности, может потребоваться для построения счетчика по модулю n.

Загрузка может быть как синхронной, так и асинхронной: в устройствах `160-`163 используется синхронная загрузка. Это означает, что ввод данных в счетчик производится по очередному перепаду тактового импульса при условии, что на линии ЗАГРУЗКА действует разрешающий сигнал. Счетчики `190-`193 являются асинхронными, или асинхронно загружаемыми; это значит, что информация вводится в счетчик при наличии разрешающего сигнала «ЗАГРУЗКА» независимо от состояния тактовой цепи. Иногда используется термин «параллельная загрузка», так как все биты загружаются одновременно.

Функция СБРОС (или УСТАНОВКА в «0») является формой предустановки. В большинстве счетчиков вход СБРОС — асинхронный, хотя в некоторых типах используется синхронный СБРОС (например, `162/163).

Прочие особенности счетчиков. В некоторых схемах на выходных линиях используются фиксаторы, которые всегда являются «прозрачными фиксаторами», и следовательно, счетчик может использоваться так, как если бы защелки не было (следует помнить, что любой счетчик с параллельными входами может работать как защелка, однако при этом нельзя одновременно производить счет и хранить информацию). Иногда очень удобно иметь счетчик в сочетании с фиксатором, например в том случае, когда после начала нового цикла счета необходимо воспроизвести или вывести предыдущее значение. В частотомере это позволяет получить устойчивую индикацию с корректировкой после каждого цикла отсчета и не воспроизводить на индикаторе все текущие состояния счетчика, сбрасывая его в нуль после окончания каждого цикла.

Имеются счетчики с выходами на 3 состояния. Они незаменимы для применений, где цифры (или 4-разрядные группы) мультиплексируются на одну шину для отображения или передачи в другое устройство. Например, устройство 779 представляет собой 8-разрядный синхронный двоичный счетчик с выходами на 3 состояния, которые могут работать как параллельные входы. Посредством объединения линий ввода/вывода счетчик размещается в 16-контактном корпусе. Устройство `593 подобно предыдущему, но выполнено в 20-контактном корпусе.

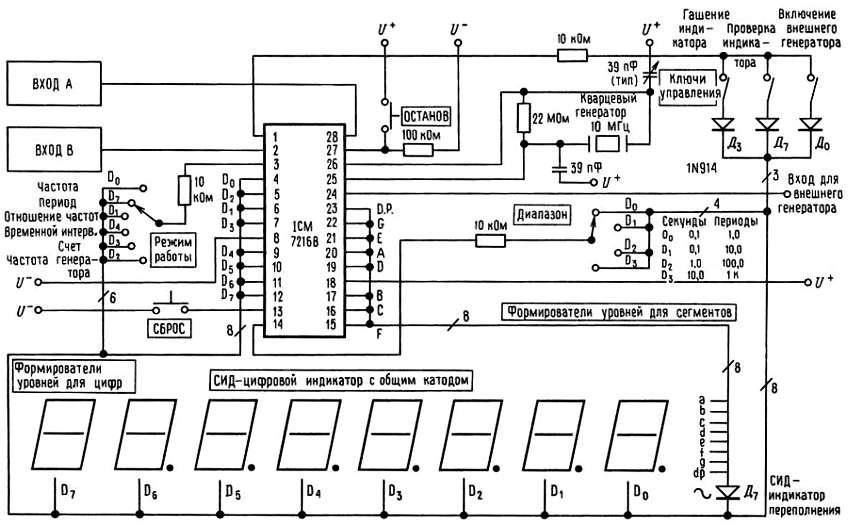

Если вы захотите использовать счетчик вместе с индикатором, то к вашим услугам несколько устройств, объединяющих в одном кристалле счетчик, регистр, 7-сегментный дешифратор и формирователь уровней для управления индикатором. Например, серия 4-разрядных счетчиков 74С925-74С928. Выпускается также схема TIL 306/7, представляющая собой счетчик и индикатор на одном кристалле. Стоит посмотреть на этот прибор, который считает и высвечивает отдельные цифры! На рис. 8.71 показана очень удачная БИС счетчика, которая не требует большого числа дополнительных компонентов.

Рис. 8.71. 8-знаковый универсальный однокристальный счетчик на 10 мГц типа Intersil 7216

(с разрешения фирмы Intersil Inc.)

В табл. 8.10 в конце главы представлены данные большинства счетчиков-кристаллов, которые вы можете использовать. Многие из них находятся только в одном семействе (например, LS или F), так что обязательно проверьте по справочнику перед проектированием.

8.26. Регистры сдвига

Если несколько триггеров соединить так, что выход Q каждого предыдущего триггера будет управлять D-входом последующего, а все тактовые входы будут возбуждаться одновременно, то получится схема, которую называют «регистр сдвига». По каждому тактовому импульсу комбинация «нулей» и «единиц» в регистре будет сдвигаться вправо, а слева через D-вход первого триггера будет вводиться новая информация. Как и во всех триггерных схемах, информация на левом входе, присутствующая непосредственно перед возникновением тактового импульса, будет введена в регистр, и на выходе будет обычная задержка распространения. Таким образом, регистры можно объединить каскадно, не ожидая возникновения режима логических гонок.

Регистры сдвига широко используются для преобразования данных из параллельной формы (n бит поступает одновременно по n независимым линиям) в последовательную (биты один за другим передаются по информационной линии) и наоборот. Они также применяются в качестве запоминающих устройств, особенно в тех случаях, когда данные считываются и записываются всегда одинаковым образом. Регистры сдвига, как и счетчик, и фиксаторы, представлены большим числом разнообразных модификаций. Все наиболее важные моменты, связанные с регистром сдвига, будут рассмотрены ниже.

Объем. 4-разрядные и 8-разрядные регистры являются стандартными. Выпускаются также регистры и с большим объемом (64 бита и больше). Существуют даже регистры с переменной длиной (например, схема 4557 может изменять свою длину от 1 до 64 бит с помощью 6-разрядного входа управления).

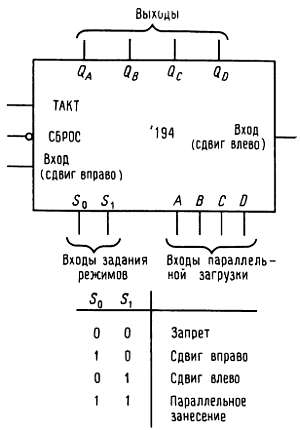

Организация. Обычно регистры сдвига являются одиночными, однако выпускаются также сдвоенные, счетверенные и сшестеренные регистры. Большинство регистров сдвига производят сдвиг только вправо, но существуют и регистры со сдвигом в обоих направлениях, такие как `194' и `323', которые имеют вход «направление» (рис. 8.72). Остерегайтесь хитростей типа «двунаправленности» у схемы `95': регистр может сдвигать влево только, если соединить предварительно каждый выход с предыдущим входом, затем произвести параллельную загрузку.

Рис. 8.72. 4-разрядный реверсивный регистр сдвига типа 74LS194.

Входы и выходы. Небольшие регистры сдвига могут производить параллельный ввод и вывод, и обычно это делают, например, схема `395' является 4-разрядным регистром сдвига с параллельным вводом и выводом (ΡΙ/ΡΟ) с выходом на 3 состояния. Большие регистры могут осуществлять только последовательный ввод и вывод, т. е. только ввод в первый триггер или вывод из последнего допускается. В некоторых случаях выводятся несколько промежуточных выходов. Единственный способ разместить как параллельный ввод, так и параллельный вывод в одном малом корпусе — это использовать одни и те же контакты в качестве входов и выходов. Так, например, схема `299 представляет собой 8-разрядный регистр параллельного ввода/вывода (ΡΙ/ΡΟ) в 20-контактном корпусе. Некоторые сдвиговые регистры включают защелки (фиксаторы) на входе или выходе, так что сдвиг может происходить пока данные загружаются или выгружаются. Так же как и у счетчиков, параллельная ЗАГРУЗКА и ОЧИСТКА могут быть либо синхронными, либо асинхронными, например схема `323 подобна схеме `299, но с синхронной очисткой.

В табл. 8.11 в конце главы приводится список сдвиговых регистров. Как всегда, не все типы регистров присутствуют во всех логических семействах, проверяйте по справочникам.

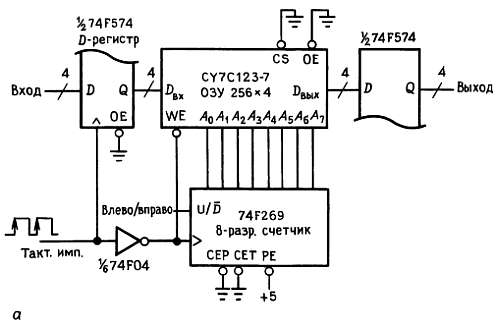

ОЗУ в качестве сдвиговых регистров. Запоминающее устройство с произвольной выборкой можно всегда использовать как сдвиговый регистр (но не наоборот), используя внешний счетчик для генерации последовательных адресов. Эта идея показана на рис. 8.73.

Рис. 8.73. Регистр сдвига большой длины на ОЗУ и счетчике; косая черточка указывает на кратность линий, в данном случае имеется 4-разрядный канал данных (а); временная диаграмма для определения максимальной частоты синхронизации при наихудшем распределении временных параметров (б); вычисления, показывающие наихудшее распределение задержек в одном такте синхронизации (в).

8-разрядный синхронный реверсивный счетчик вырабатывает последовательность адресов для КМОП ОЗУ с организацией 256x4 бит. Такая комбинация ведет себя подобно четырем 256-бит сдвиговым регистрам с направлением сдвига вправо/влево, выбираемым управляющей линией ВВЕРХ/ВНИЗ счетчика. Все остальные входы, как показано на рисунке, служат для разрешения счета. Выбирая быстрые счетчики и память, мы можем достигнуть максимальной скорости 30 МГц (см. временную диаграмму), которая такая же, как и у интегральных (не на много меньше) сдвиговых регистров НС-типа. Этот метод может быть использован для получения очень большого регистра сдвига, если требуется.

Упражнение 8.28. В схеме на рис. 8.73 кажется, что входные данные поступают в ту же ячейку, что и выходные данные при чтении. Тем не менее схема ведет себя подобно классическому сдвиговому регистру на 256 слов. Объясните, почему.

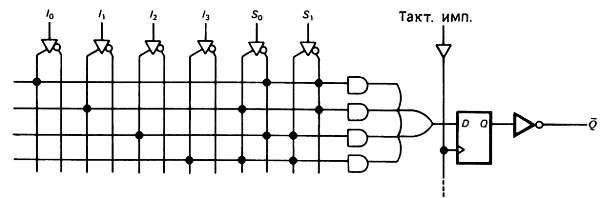

8.27. Последовательностные ПМЛ

Комбинационные (только на вентилях) ПМЛ, которые мы рассматривали выше в разд. 8.15, входят в большое семейство, которое включает устройства с различным числом регистров D-типа на кристалле (называемые «регистровые ПМЛ»). Типичный из этих ПМЛ-16R8-показан на рис. 8.74.

Рис. 8.74. Регистровая ПМЛ 16R8 имеет 8 внешних входов, 8 выходов, линии синхронизации и управления 3-м состоянием. Выходы регистра можно также использовать как входы матрицы И.

(с разрешения фирмы Advanced Micro Devices, Калифорния.)

Программируемая — И/фиксированная ИЛИ матрица типовых комбинационных ПМЛ генерирует входные уровни для 8 синхронно тактируемых регистра D-типа с выходами на 3 состояния; выходы регистра (прямой и инверсный) как и стандартные входные контакты доступны как входы логической матрицы.

Если вы посмотрите снова на рис. 8.57, вы увидите, что ПМЛ с регистрами — это элемент последовательностной схемы общего назначения с определенными ограничениями на число регистров и вентилей, и вы можете конструировать, что хотите, но только в этих пределах. Например, вы можете сделать сдвиговой регистр или счетчик, или сразу оба. На практике вы можете сделать некоторый кусок логики как часть большой схемы, для которой альтернативой является дискретная логика, построенная на вентилях и триггерах. Посмотрим некоторые примеры.

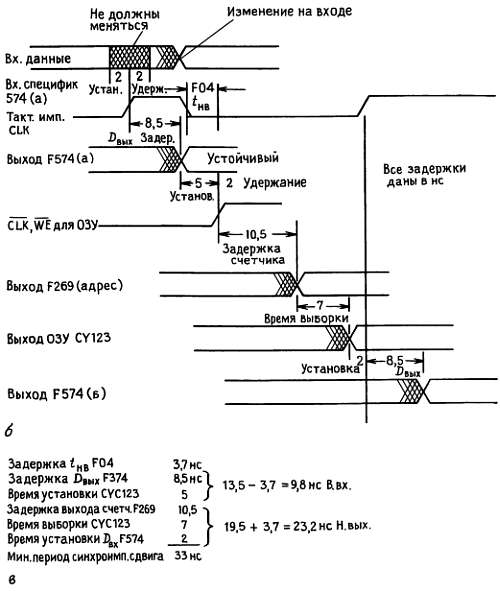

Карты перемычек, создаваемые вручную. Простые проекты могут конструироваться в ПМЛ посредством изображения логики, затем соответствующий образ преобразуется в массив перемычек для программатора ПМЛ. Так, например, предположим, что мы хотим получить 4-входовый мультиплексор с защелкиваемыми выходами. Мы можем записать логическое уравнение для мультиплексной части (т. е. до D-входов триггера) в виде

Q.d = I0*S'0*S'1 + I1*S0*S'1 + I2*S'0*S1 + I3*S0*S1

где входы S0 и I1 - адреса, выбирающие входы I0-S3 и «*» и «+» соответственно И или ИЛИ.

Регистровые ПМЛ легко реализуют это с фиксацией результата. Заметим, что мы использовали ИЛИ 3-входовых И, предпочитая это первоначальному декодированию выбранного адреса на двухвходовых вентилях И, так как мы вынуждены использовать сумму произведений (это также быстрее). Окончательная схема показана на рис. 8.75 (заметим, существует тонкость для этой схемы, см. подразд. «Выбросы» в конце этого раздела).

Рис. 8.75. 4-входовый мультиплексор с фиксацией, выполненный на ПМЛ.

PALASM. Для схем какой-либо разумной сложности необходимы некоторые методы логического проектирования ПМЛ. Например, ПМЛ 16L8 имеет 2048 перемычек, а сложный проект может потребовать, чтобы вы прожгли несколько сотен из них, и если вы не необычайно обязательны, то маловероятно, что достигните цели вручную, корректно определив их для ПМЛ-программатора. PALASM (PAL Assembler, торговый знак фирмы Monolithic Memories Inc.), разработанный фирмой Monolithic Memories (впервые создавшей ПМЛ), был одним из первых инструментов. Он берет логическое выражение, подобное тому, которое мы писали выше, и преобразует его в карту перемычек. Производится это посредством программы, но без логической минимизации, поэтому вы должны проделать эту трудную работу сами. Однако PALASM позволяет вам вводить набор тестовых состояний (называемых тестовыми векторами), дающих возможность получить на выходах то, что должно быть результатом ваших логических спецификаций. Таким образом вы можете отлаживать ваши уравнения перед изготовителем ПМЛ.

PALASM широко используется. Существуют листинги исходных текстов (кодов) на языке Фортран, которые могут затем послать карты перемычек для ПМЛ-программаторов (в стандартном «JEDEC»-фopмате) через последовательный порт. Многие ПМЛ-программаторы со встроенными микропроцессорами включают резидентный PALASM такие, например, как у фирм Data I/O, Digiles, Stag, и Structured Resign. Остается только подключить терминал, и вы в работе.

Языки ABEL и CUPL. PALASM — помощник, но серьезному пользователю ПМЛ необходимо большее. Языки логического программирования высокого уровня подобно языкам ABEL (фирмы Data I/O) и CUPL (фирмы Logical Devices) делают программирование ПМЛ (и ПЛМ) легкой работой. Они позволяют вам задавать логику либо через логические булевы уравнения, либо через таблицы истинности, для последовательностных схем вы задаете состояния и правила перехода. Подобно какому-либо хорошему языку высокого уровня, вы можете определять массивы (для набора сигналов, т. е. адресной шины), выражения и промежуточные значения, затем использовать их в других выражениях. Эти языки достаточно «умны» для преобразования таблиц истинности в логические выражения с последующей минимизацией их (также, как и логических булевых выражений) в логически идентичные, окончательный результат получается в форме, которая соответствует логическим ограничениям устройства (т. е. сумма произведений для ПМЛ). Вместо записи сверху вниз явнозаданных логических выражений для ряда значений вам достаточно записать что-то вроде ADDR: [10…FF], которое будет преобразовано в соответствующую логику. Эти языки также позволяют вам определять тест-векторы, с помощью которых тестируется ваша схема, кроме того, тест-векторы могут также посылаться в программатор для проверки запрограммированного кристалла. Наконец, эти языки позволяют получить стандартную документацию на законченный кристалл, что существенно, если вы захотите отлаживать приспособление с этими самодельными устройствами.

С целью конкретизации этих идей, давайте рассмотрим оба примера проектирования как последовательностных, так и комбинационных схем, используя язык CUPL.

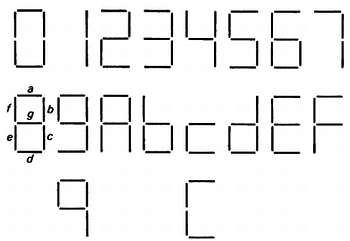

Пример использования языка CUPL для проектирования преобразователя из 7-сегментного кода в шестнадцатеричный (комбинационная логика). Наступает время, когда вы захотите использовать желаемый БИС-кристалл, который выполняет определенную функцию (например, калькулятор или хронометр), как часть создаваемого вами устройства. Беда в том, что эти БИС-кристаллы обычно имеют выходы для прямого управления 7-сегментным индикатором, который предпочтительней, чем шестнадцатеричные (или двоичные) выходы, которые вы хотите получить. Давайте спроектируем кристалл-шифратор, который преобразует 7-сегментный код обратно в 4-битовый двоичный, такая функция не реализуется как стандартная микросхема (хотя существует дешифратор из семисегментного кода в двоично-десятичный, 74С915).

Входы представляют отдельные сегментные сигналы, которые всегда помечаются символами a — f (рис. 8.76).

Рис. 8.76. Коды 7-сегментного индикатора.

На рис. 8.76 показано, как цифры представляются на 7-сегментном индикаторе. Заметьте, что возможно двоякое представление «9» и «С», оба из которых должны корректно восприниматься вашей логикой. Для ПМЛ мы выбираем X6L8, 20-контактная комбинационная часть которой логически была показана на рис. 8.45.

Рис. 8.77 представляет входное описание на языке CUPL. Здесь сигналы запуска сегментов а — g обозначают входы (положительная логика), а шестнадцатеричные разряды D0-D3 выходы (отрицательная логика). Язык CUPL позволяет определить промежуточные переменные, которые могут быть использованы в выражениях позднее. В этом случае удобно определить очевидные переменные от zero до next через возможные отображения цифры в терминах сегментных входов. Это просто большие термы произведений (И) от входных сегментных переменных, которые вы можете прочесть из изображений цифр на рис. 8.76.

/** Inputs **/

PIN 1 = a; /* segment a */

PIN 2 = b; /* segment b */

PIN 3 = c; /* segment c */

PIN 4 = d; /* segment d */

PIN 5 = e; /* segment e */

PIN 6 = f; /* segment f */

PIN 7 = g; /* segment g */

/** Outputs **/

PIN 19 = !D3; /* msb of hex encode */

PIN 18 = !D2; /* */

PIN 17 = !D1; /* */

PIN 16 = !D0; /* 1sb */

/** Declarations and Intermediate Variable Definitions **/

zero = a & b & c & d & e & f & !g;

one = !a & b & с & !d & !e & !f & !g

two = a & b & !с & d & e & !f & g;

three = a & b & c & d & !e & !f & g;

four = !a & b & с & !d & !e & f & g;

five = a & !b & с & d & !e & f & g;

six = a & !b & c & d & e & f & g;

seven = a & b & с & !d & !e & !f & !g;

eight = a & b & c & d & e & f & g;

nine = a & b & с & !d & !e & f & g

# a & b & c & d & !e & f & g; /* two ways */

hexa = a & b & с & !d & e & f & g;

hexb = !a & !b & c & d & e & f & g;

hexc = !a & !b & !c & d & e & !f & g

# a & !b & !c & d & !e & f & !g; /* two ways */

hexd = !a & b & c & d & e & !f & g;

hexe = a & !b & !c & d & e & f & g;

hexf = a & !b & !c & !d & e & f & g;

/** Logic Equations **/

D3 = eight # nine # hexa # hexb # hexc # hexd # hexe # hexf;

D2 = four # five # six # seven # hexc # hexd # hexe # hexf;

D1 = two # three # six # seven # hexa # hexb # hexe # hexf;

D0 = one # three # five # seven # nine # hexb # hexd # hexf

Рис. 8.77. Спецификация преобразователя 7-сегментного представления в 16-ричное на языке CUPL.

Окончательно каждый двоичный выходной бит записывается как сумма (ИЛИ) цифровых переменных, при которых этот бит устанавливается. Мы используем уровни отрицательной логики, потому что 16L8 представляет матрицу И-ИЛИ-НЕ. Этим заканчивается логическая спецификация для языка.

Упражнение 8.29. Проверьте для себя правильность нашей работы, записав некоторые из отображаемых символов, через заданные нами промежуточные переменные zero-next.

Язык CUPL сначала использует определение промежуточных переменных для записи выражений D0-D3 прямо в термах входных переменных a — f, работа, которая подобно ассемблеру PALASM должна исполняться нами изначально. В этом случае логические уравнения представлены в желательной И-ИЛИ-НЕ форме. Однако мы не закончили на этом, так как 16L8 (и все другие комбинационные ПМЛ) допускают не более 7 термов произведений для каждой суммы, тогда как мы имеем 9, 8, 9 и 10 соответственно для выходов D0-D3. Одним решением может быть связывание выхода через вторичный вентиль ИЛИ, для того чтобы получить желательное число термов произведений в сумме.

Эта обычно рассматриваемая форма плоха, так как она удваивает задержки распространения, хотя это не так важно в медленных устройствах, подобных этому. Лучшее решение — произвести логическую минимизацию, используя логическую эквивалентность по формуле Моргана, например.

Мы запускаем минимизатор CUPL, который выдает термы произведений (рис. 8.78).

** Expanded Product Terms **

D0 =>

a & b & c & d & !e & g

# a & b & с & !e & f & g

# a & с & d & !e & f & g

# b & с & !d & !e & !f & !g

# !a & !b & c & d & e & f & g

# a & !b & !c & !d & e & f & g

# !a & b & c & d & e & !f & g

D1 =>

a& !b & !c & e & f & g

# !b & c & d & e & f &g

# a & b & с & !d & e & f & g

# a & b & !c & d & e & !f & g

# a & b & c & d & !e & !f & g

# a & b & с & !d & !e & !f & !g

D2 =>

а & !b & !с & d & е & f

# а & !b & c & d & f & g

# а & !b & !с & е & f & g

# !а & b & с & !d & !е & f & g

# !a & b & c & d & e & !f & g

# !a & !b & !c & d & e & !f & g

# a & b & с & !d & !e & !f & !g

D3 =>

a & b & c & f & g

# a & !b & !c & d & e & f

# a & !b & !c & e & f & g

# !a & !b & c & d & e & f & g

# !a & b & c & d & e & !f & g

# !a & !b & !c & d & e & !f & g

D0.oe => 1

D1.oe => 1

D2.oe => 1

D3.oe => 1

Рис. 8.78. Преобразователь 7-сегментного представления в 16-ричное с минимизированными термами произведения.

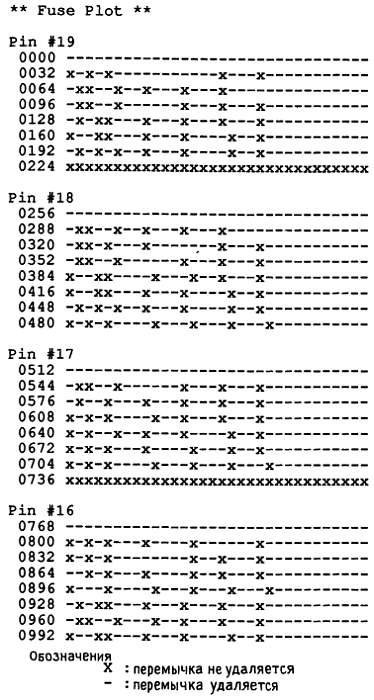

Взгляните, все удовлетворяет ограничению «7 произведений». CUPL также рисует для вас карту перемычек (рис. 8.79).

Рис. 8.79. Карта перемычек преобразователя 7-сегментного представления в 16-ричное.

Конечно, вы не программируете ПМЛ так, а используете вместо этого прямую загрузку универсального JEDEC программирующего формата. В этом примере язык CUPL, очевидно, делает трудную задачу простой.

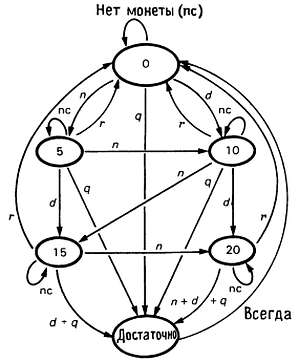

Пример использования языка CUPL для программирования автомата-продавца (последовательная схема). Произвольная машина состояний (разд. 8.18) имеет набор состояний и правил перехода для движения между этими состояниями по каждому фронту синхроимпульса. Правила перехода зависят от текущего состояния и от частной комбинации входных уровней, существующих на следующем фронте. Вы можете соорудить машину состояний на программируемой логике, содержащей регистры, если а) существует достаточное число битов в регистре для представления всех возможных состояний (например, с 4-разрядным регистром вы можете иметь до 16 состояний), и б) существует достаточное число входов и логических вентилей для реализации правил перехода.

Как пример, давайте спроектируем регистровую ПМЛ для диаграммы состояний на рис. 8.80.

Рис. 8.80. Диаграмма состояний торгового автомата.

Это — торговый автомат, предназначенный для выдачи бутылки сладкой шипучей жидкости, когда опущено 25 цент или более. Существует некоторый вид монетного интерфейса, который «заглатывает», распознает монету и посылает на наш ПМЛ 2-битовый входной сигнал (С1, С0), действительный для одного такта, показывающего монету, которую опустили (01-5 цент, 10–10 — цент монета, 11–25 — цент монета, 00 — нет монеты). Задача машины состояний добавлять к общему вкладу и формировать выход, называемый «бутылка», когда опущено достаточно монет. Рис. 8.81 показывает спецификацию, выполненную в синтаксисе машины состояний языка CUPL.

/** Inputs **/

Pin = elk; /* clock — positive edge */

Pin = c0; /* coin type — low bit */

Pin = c1; /* coin type — high bit */

Pin = reset; /* reset input */

/** Outputs **/

Pin 18 = !Q0; /* bit 0 of state variable */

Pin 17 = !Q1; /* bit 1 */

Pin 16 = !Q2; /* bit 2 */

Pin 15 = !bottle; /* bottle disgorge command */

/* Define machine states with symbolic names;

"enough" = 25 cents or more */

$define S0 'b'000

$define S5 'b'001

$define S10 'b'010

$define S15 'b'011

$define S20 'b'100

$define ENOUGH 'b'101

/* define intermediate variables */

nocoin = !c0 & !c1 & !reset;

nicke1 = c0 & !c1 & !reset;

dime = !c0 & c1 & !reset;

quarter = c0 & c1 & !reset;

/* Define state bit variable field */

field statebit = [Q2..0];

/* Transition rules for vending machine */

sequence statebit {

present S0 if nocoin next S0;

if nicke1 next S5;

if dime next S10;

if quarter next ENOUGH out bottle;

present S5 if nocoin next S5

if nicke1 next S10;

if dime next S15;

if quarter next ENOUGH out bottle;

present S10 if nocoin next S10

if nicke1 next S15;

if dime next S20;

if quarter next ENOUGH out bottle;

present S15 if nocoin next S15

if nicke1 next S20;

if dime next ENOUGH out bottle;

if quarter next ENOUGH out bottle;

present S20 if nocoin next S20

if nicke1 next ENOUGH out bottle;

if dime next ENOUGH out bottle;

if quarter next ENOUGH out bottle;

present ENOUGH next S0; }

Рис. 8.81. Спецификация торгового автомата на языке CUPL.

Как и прежде, мы начнем с определения входных-выходных контактов. Заметим, что мы добавили вход reset (сброс) так, чтобы вы могли перейти к начальному состоянию S0 (нет монеты). Затем мы определим состояния, потом правила перехода между ними. Если какие-либо выходы, либо регистровые, либо комбинационные, необходимо генерировать в течение состояний или переходов между состояниями, они определяются в то же самое время. В этом примере выход «бутылка» специфицируется как раздельный выходной регистр, т. е. выходные состояния дешифрировать не нужно. Фактически нужен только выход, а биты Q0-2 машины состояний могут быть представлены во внутренних регистрах, которые не генерируют прямо выводы; некоторые программируемые логические устройства имеют также внутренние регистры в дополнение к обычным выходным регистрам.

Заметим, что вы должны определить точно переход из некоторого состояния в себя, также, как мы делали для входа «нет монеты». Неопределенное условие безусловно сбрасывает состояние во все нули. Это происходит потому, что эти условия собираются в комбинационную логику для выставления на D-входы регистров и, таким образом, если условие не удовлетворяется, то соответствующий D-вход не подтверждается. Рис. 8.82 показывает вывод из языка CUPL.

** Expanded Product Terms **

Q0.d =>

!Q0 & !Q1 & cQ & !reset

# !Q0 & !Q2 & cO & !reset

# Q0 & !Q2 & !c0 & !reset

# Q0 & !Q2 & c1 & !reset

# !Q0 & !Q1 & Q2 & c1 & !reset

Q1.d =>

!Q1 & !Q2 & !c0 & c1 & !reset

# !Q0 & Q1 & !Q2 & !c1 & !reset

# Q1 & !Q2 & !c0 & !c1 & !reset

# Q0 & !Q1 & !Q2 & cO & !c1 & !reset

Q2.d =>

!Q0 & !Q1 & Q2 & !reset

# Q1 & !Q2 & c1 & !reset

# !Q2 & c0 & c1 & !reset

# Q0 & Q1 & !Q2 & c0 & !reset

bottle.d =>

!Q2 & c0 & c1 & !reset

# !Q0 & !Q1 & Q2 & c0 & !reset

# !Q0 & !Q1 & Q2 & c1 & !reset

# Q0 & Q1 &!Q2 & c1 & !reset

statebit =>

Q2, Q1, Q0

Рис. 8.82. Выход CUPL для торгового автомата.

Ничего очевидного или простого в логике, поскольку и состояние автомата (S0-S5) и входящие переменные (С0-1) определены в виде двоичных чисел, а логика работает по отдельным битам. Таким образом, результирующая логика не сильно связана с первоначальным описанием состояний (рис. 8.81). Фактически, конкретный выбор состояний (возрастающий двоичный код 0–5) мог бы быть различным, это полностью изменило бы результирующую логику. В этом случае этот пример легко укладывается в ограничениях ПМЛ 16R6 (8 термов произведений на регистр): если это не так, мы могли бы попытаться переопределить состояния, что часто приводит к более простой логической реализации. Заметим, что вход сброса действует, заменяя безусловность всех D-входов, которую мы задали посредством нашего задания промежуточных переменных «нет монеты», «5 цент» и т. д.

Упражнение 8.30. Проконтролируйте правильность конечных логических выражений, посредством проверки нескольких правил перехода. Вы должны испытать все переходы от 00, или от «5 центов», или «10 центов» к какому-либо другому состоянию.

Упражнение 8.31. Хорошие торговые автоматы имеют размен. Перерисуйте диаграмму состояний (рис. 8.80) так, чтобы были состояния (сколько?) для каждого возможного числа разменов. Модифицируйте правила перехода соответственно. Гарантируйте, чтобы ваш усовершенствованный автомат выполнял свою основную работу — выдачу бутылок.

Упражнение 8.32. Нарисуйте диаграмму состояний и правил перехода для электронного комбинационного замка. Он должен открываться только тогда, когда четыре цифры набраны в правильном порядке. Какая-либо ошибка должна сбрасывать его.

Возможные применения программируемых логических интегральных схем (ПЛИС)

Для выполнения некоторых функций ПЛИС подходит как нельзя лучше. Вот самые важные области применения и преимущества ПЛИС:

Автоматы. Как и в предыдущем примере, ПЛИС естественным образом вписывается в произвольный синхронный автомат. Было бы неразумно использовать матрицу из D-триггеров и дискретную комбинационную логику, когда ПЛИС способна выполнить те же функции в одном недорогом и мощном корпусе.

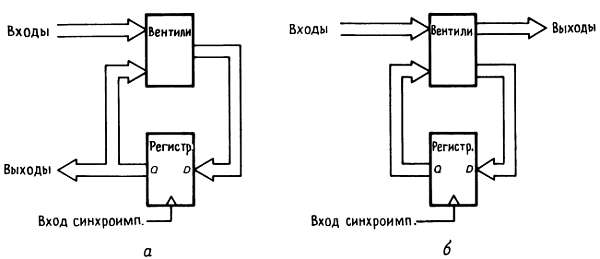

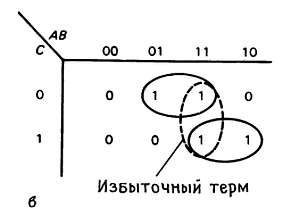

Замена произвольной логики. Во многих схемах вы можете обнаружить узлы и клубки из вентилей, инверторов и триггеров, называемых с пренебрежением «произвольная логика» или «клей». ПЛИС обычно сокращает число корпусов в 4 и более раз. Кроме того, при использовании ПЛИС схема становится более понятной, поскольку применение большого числа вентилей означает, что всю необходимую вентильную обработку можно сделать при вводе в регистры (при этом выходы становятся строго синхронными) вместо того, чтобы комбинировать выходы регистра с вентилями (при этом выходы не будут строго синхронными); см. рис. 8.83.

Рис. 8.83. Программируемое логическое устройство (а); обычная дискретная логика (б).

Гибкость. В ряде случаев вы не совсем представляете себе, как, в конце концов, должна работать ваша схема, тем не менее вы должны как-то ее завершить, чтобы иметь возможность с ней «поиграть». Здесь ПЛИС как раз к месту, так как в отличие от дискретной логики на некотором этапе вы имеете возможность заменить одну на другую без перемонтажа. Схемы на ПЛИС приобретают характер программ.

Несколько версий. С помощью ПЛИС можно спроектировать одну единственную схему и затем изготавливать несколько различных версий устройства, выпуская платы с различно запрограммированными ПЛИС. Например, вы могли бы иметь компьютер, который содержит кристаллы памяти либо на 256К, либо на 1М, причем изменения касались бы только ПЛИС.

Скорость и комплектация. При использовании ПЛИС проектирование схемы в общем случае можно выполнить гораздо быстрее (если вы, разумеется, хорошо ориентируетесь в этой области). Более того, вам потребуется всего несколько типов ПЛИС, а не несколько дюжин типов стандартных схем средней интеграции. Действительно, всего две новых ПЛИС GAL (базовая матричная логика) благодаря программируемости своей внутренней архитектуры (и связей) заменят целый набор ПМЛ. В частности, 20-выводная GAL16V8 и 24-выводная GAL20V8 каждая может имитировать по 21 стандартных ПМЛ. Более того, их можно запрограммировать как «помесь» ПМЛ (например, нечетное число регистров).

Расширение функций ПМЛ. Входы/выходы. Выводы выходов с 3 состояниями, подключенные внутри кристалла к входам матрицы И, можно использовать в качестве входов. Например, ПМЛ 16L8, показанная на рис. 8.45, имеет 16 входов (прямых и инверсных) на матрицу И; 10 из них обозначены как входные выводы, а 6 являются цепями обратной связи с выходов с 3 состояниями. Эти 6 выводов можно превратить в «перманентные» входы путем блокировки соответствующего выхода (подключить пару прямой/инверсный к управлению И); с другой стороны, эти входы могут работать в двух направлениях за счет блокировки формирователей с 3 состояниями, соответствующими некоторой логической переменной.

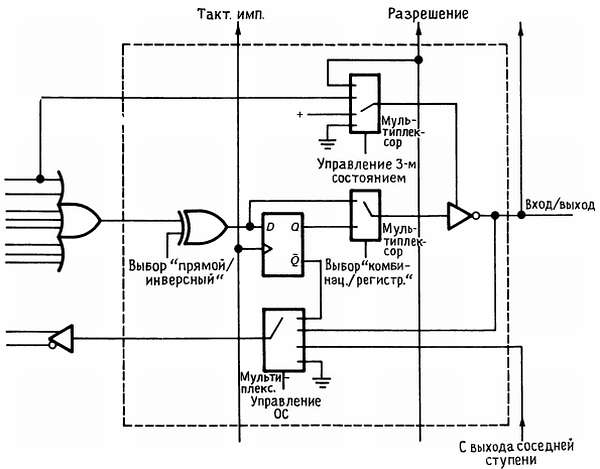

«Супер-ПМЛ». Ранее мы уже отмечали, что наиболее гибкая программируемая логика соответствует оригинальным ПМЛ, среди которых самыми известными являются стираемые КМОП-варианты фирм Lattice, VTI, Altera и др. ПМЛ GAL фирмы Lattice, например, использует программируемую логику с электрическим стиранием, так что вы можете перепрограммировать кристалл. Более того, выходные структуры («макроячейки») сами программируемы, — каждый выход может быть как регистром, так и комбинационной схемой с прямым и инверсным выходом. Похожей программируемостью обладают линия активации 3-го состояния и линия включения обратной связи (последняя может подключаться до и после буфера с 3 состояниями или к соседнему выходу); см. рис. 8.84. В результате, вы можете имитировать любую обычную 20-выводную ПМЛ, используя только один корпус GAL16V8 (и любую обычную 24-выводную ПМЛ, используя GAL20V8). Это позволяет сохранять перечень комплектующих изделий в управляемых границах. Фирма Altera имеет линию программируемой КМОП-логики, которая допускает ультрафиолетовое стирание по типу ЭППЗУ (в корпусе ИС над кристаллом имеется окно из кварцевого стекла). Такие устройства называют СПЛИС — стираемая программируемая логическая интегральная схема.

Рис. 8.84. Программируемая макроячейка базовой матричной логики.

Самая маленькая ИС из этой серии (ЕР320) имеет выходные макроячейки и имитирует все 20-выводные ПМЛ, точно также, как GAL16V8. Более того, она маломощна в отличие от «прожорливых» оригинальных ПМЛ (см. ниже). Наконец, фирма Altera выпускает несколько более крупных СПЛИС, а также программируемые микросеквенсеры и т. п. Фирмы Cypress и VTI также выпускают стираемую программируемую КМОП-логику с макроячейками. Другим подходом к созданию программируемой логики является ОЗУ-подобная вентильная матрица фирмы Xilinx. Впечатляющие кристаллы этой матрицы содержат огромные блоки конфигурируемой логики, причем конфигурация связей хранится во внутреннем ОЗУ кристалла (энергозависимая память). Эта память загружается от внешней памяти после включения питания либо от микропроцессора; кроме того, она может самозагружаться с использованием памяти типа энергонезависимого ПЗУ.

Скорость и мощность. Оригинальная ПМЛ на биполярных транзисторах, разработанная на фирме Monolithic Memories (и быстро скопированная National и AMD) потребляла значительный ток — около 200 мА для 16L8/16R8, и имела задержку распространения 40 нс. Последующие биполярные ПМЛ «половинной мощности» были вполне приемлемы — 90 мА и 35 нc. Однако самые быстрые ПМЛ потребуют все еще уйму мощности; например, время распространения ПМЛ 16R8D и 16Р8-7 фирмы AMD составляет соответственно 10 и 7,5 нс, но потребляют они 180 мА. (макс). КМОП-приборы существенно лучше: GAL (GAL20V8-15Q) «1/4 мощности» фирмы Lattice потребляют 45 мА при задержке 15 нс, ЕР320-1 фирмы Altera обладают задержкой 25 нс при токе 5 мА. Но что более важно для маломощных устройств, так это то, что кристаллы фирмы Altera (а также ПМЛ серии Ζ фирмы AMD) могут работать в резервном режиме с «нулевой мощностью». Конструкторы будущих структур программируемой логики, наверняка, сохранят эту здоровую тенденцию к повышению скорости и снижению мощности; современная программируемая логика, этот «пожиратель ватт», начинает уходить в прошлое!

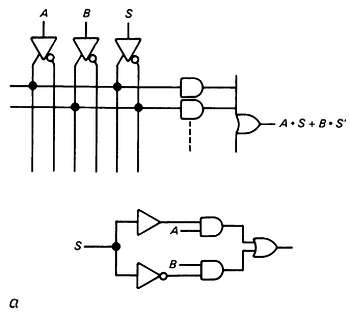

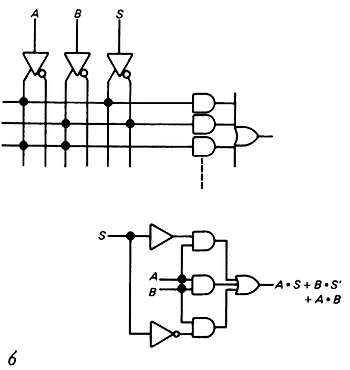

Выбросы. ПЛИС, конечно, удивительная вещь, но вы можете, ненароком, оказаться в затруднительном положении, если не будете помнить о возможности логических состязаний. На рис. 8.85 показан 2-входовый мультиплексор, выполненный самым обычным способом; показаны ПМЛ — реализация и эквивалентная схема.

Рис. 8.85. Исключение глитча в ПМЛ; а — 2-входовый мультиплексор; б — для исключения глитча добавляется избыточный терм произведения; в — карта Карно с избыточным термом.

Здесь все выглядит как-будто прекрасно, но схема имеет один изъян: когда оба входа (А и В) находятся в состоянии высокого уровня, а линия ВЫБОР меняет состояние, на выходе, как показано, возможен выброс. Это объясняется тем, что внутренние задержки по цепям S и S' могут быть не равны, что приведет к появлению переходного состояния, в котором на одном из входов вентилей И будет низкий уровень. Избавиться от этого можно, использовав избыточный терм А*В, который будет гарантировать отсутствие выбросов, в чем вы можете легко убедиться.

Упражнение 8.33. Покажите, что дополнительный терм устраняет все возможности для появления выбросов.

Упражнение 8.34. Какие логические термы следует добавить к 4-входовому мультиплексору (рис. 8.75) для устранения выбросов.

С помощью карт Карно вы можете наглядно убедиться в существовании этих так называемых логических рисков; карта Карно для 2-входового мультиплексора рис. 8.85, а приведена на рис. 8.85, в. Каждая группа на карте представляет один терм произведения, который образует вход вентиля ИЛИ. Истинное значение на выходе ИЛИ появляется в том случае, когда любой из термов произведения имеет истинное значение; но переход между группами произведений может приводить к выбросам, если переменные первой группы снимаются, до того, как будут назначены переменные второй группы.

«Противоядие» (которое мы использовали и ранее) состоит в добавлении избыточных термов, гарантирующих, что любые переходы между логическими «1» будут включены в один терм произведения. Другими словами, любые единицы, которые лежат в соседних рядах или столбцах, будут покрыты группой произведения. Это предписание можно дать в обобщенной форме, связанной непосредственно с булевым логическим выражением, а не с картой Карно. Это удобно для логических функций, зависящих от более, чем 4-х переменных.

В предыдущем примере представлены так называемые статические выбросы, поскольку выход будет оставаться статическим. Существуют также динамические выбросы, проявление которых заключается в том, что выход, который должен сделать один-единственный переход, начинает многократно переходить из состояния в состояние. При использовании программируемой логики можно избежать этих внутренних гоночных условий. В общем средства проектирования такие, как PALASM, ABEL и CUPL не пытаются решать эти проблемы. Если хотите, они делают все, чтобы ухудшить ситуацию, поскольку их логические оптимизаторы усердно работают по исключению таких избыточных термов.

8.28. Разнообразные последовательностные схемы

Появление на рынке большого числа разнообразных БИС и СБИС (имеющих более 1000 вентилей на кристалле) дает возможность использовать достаточно сложные устройства, выполненные на одном кристалле. В этом разделе мы приведем несколько выборочных примеров.

Память типа «первый вошел-первый вышел» (FIFO) в некотором смысле аналогична регистру сдвига, так как информация, вводимая на входе, в том же порядке появляется на выходе. Однако между ними есть существенное отличие, которое состоит в том, что в регистре сдвига информация «проталкивается вдоль него» по мере ввода и тактирования дополнительных бит, а в запоминающем устройстве типа «первый вошел-первый вышел» данные «проваливаются насквозь» и выстраиваются в выходную очередь с очень малой задержкой. Управление вводом и выводом производится раздельными тактовыми последовательностями, а устройство помнит, какие данные введены и какие выведены. Можно провести полезную аналогию с кегельбаном, где белые и черные игровые шары (биты) возвращаются на исходную позицию. Эти биты вводятся с помощью игральной машины, а время, которое требуется шару для того, чтобы прокатиться по своему лотку, соответствует «задержке при сквозной передаче» в ЗУ типа «первый вошел-первый вышел» (обычно 1-25 мкс). После этого биты приходят на выход и могут забираться пользователем по мере надобности (т. е. асинхронно). Память типа «первый вошел-первый вышел» полезно использовать для буферизации асинхронных данных. Классическим примером является буферирование клавиатуры (или другого входного устройства, такого, как магнитная лента) ЭВМ или другого устройства обработки данных. При использовании этого метода данные не будут теряться в том случае, когда ЭВМ не готова принять очередное выработанное слово — при условии, конечно, что ЗУ незаполнено целиком. Примерами типичных устройств памяти являются 74F433 (ТТЛ, 64 слова по 4 бит каждое, 10 МГц, время «пролета» 4 мкс) и IDT7202 (КМОП, 4096x9,15 МГц, нулевое время «пролета»).

Память типа «первый вошел-первый вышел» не применяется, если устройство, которому вы посылаете данные, может всегда получить их до поступления следующих данных. На компьютерном языке — вы должны гарантировать, что максимальная латентность меньше, чем минимальное время между словами данных (время скрытости данных). Заметим, что память типа «первый вошел-первый вышел» не будет полезна, если получатель данных не готов (не способен) в среднем воспринять приходящие данные.

Умножитель частоты используется для генерации последовательности выходных импульсов с частотой, значение которой связано с тактовой частотой через рациональную дробь. Например, 3-декадный двоично-десятичный умножитель позволяет получать на выходе частоты, составляющие nnn/1000 от входной частоты; nnn-трехзарядное десятичное число, заданное тремя входными двоично-десятичными знаками. Это не то же, что счетчик по модулю n, так как с его помощью на выходе нельзя получить частоту, равную 3/10 входной. Отметим один важный момент: импульсы на выходе умножителя в общем случае не будут следовать равномерно. Они совпадают с входными тактовыми импульсами и образуют чудные комбинации, средняя частота которых задается предварительно. Примерами устройств являются `97 (6-битовый, двоичный) и `167 (двоично-десятичный).

Счетчик частоты. Фирма Intersil имеет хороший набор интегральных счетчиков частоты. Они включают средства блокировки входного сигнала для точного определения интервалов, до восьми цифр двоично-десятичного счетчика, дисплейные формирователи и т. д. Эти кристаллы обычно требуют очень мало внешней схемотехники.

Цифровые вольтметры. Вы можете получить цифровые вольтметры на одном кристалле. Они включают цепи аналого-цифрового преобразователя и необходимой синхронизации, схемы счета и управления дисплеем. Примерами таких устройств являются маломощный 3,5-разрядный АЦП ICL7136 и 4,5-разрядный АЦП ICL7129; оба используют жидкокристаллический семисегментный индикатор и работают от одной батареи 9 В.

Схемы специального назначения. Существуют прекрасные наборы БИС кристаллов для областей, подобных радиосвязи (например, синтезаторы частоты), для цифровой обработки сигналов (умножители/накопители, цифровые фильтры), корреляторы, арифметические устройства), передачи данных (универсальных), асинхронные приемопередатчики, модемы, сетевые интерфейсы, ИС кристаллографирования (декристаллографирования данных, преобразователи последовательных форматов). Часто эти кристаллы используются совместно с устройствами на базе микропроцессоров и многие из них не могут работать в одиночку.

Кристаллы для бытового применения. Полупроводниковая промышленность любит разрабатывать ИС для использования их в изделиях большого рынка. Вы можете получить однокристальные схемы для изготовления цифровых (иди «аналоговых») часов, таймеров, замков, калькуляторов, детекторов дыма, телефонных аппаратов, синтезаторов музыки, генераторов ритма и аккомпанемента и т. д. Что касается радиоприемников, телевизоров, компакт-дисков, то сейчас в этом отношении дело обстоит хуже из-за большой степени интеграции. Синтез речи (и особенно распознание речи) в последнее время получил некоторое развитие; вот почему лифты, автомобили и даже кухонные аппараты обращаются теперь к нам теми голосами, которые мы любим. Судя по всему, следующим большим шагом будет разработка эффективных автомобильных схем (для выполнения функций двигателя, систем предотвращения столкновений и т. п.).

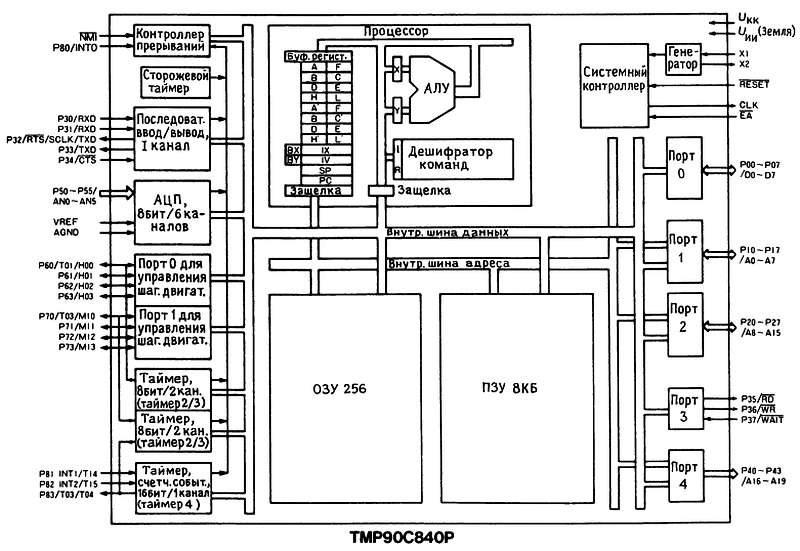

Микропроцессоры. Самым выдающимся примером «чуда» БИС является микропроцессор (компьютер на кристалле). На одной вершине находятся мощные цифровые приборы, подобные 68020/30 и 80386/486 (32-разрядные быстрые процессоры с предвыборной команд, виртуальной памятью, мощнейшие арифметические сопроцессоры) и кристаллы, подобные MicroVAX, которые эмулируют существующие большие компьютеры. На другой вершине — однокристальные процессоры с различными функциями ввода, вывода и памяти, работающие самостоятельно. Например, один из последних образцов, это TLCS-90 фирмы Toshiba (рис. 8.86), представляющий маломощный КМОП микроконтроллер с 6-канальным 8-разрядным АЦП, встроенными таймерами, ОЗУ и ПЗУ, 20-двунаправленными цифровыми линиями ввода/вывода, последовательным портом и двумя портами для управления шаговыми двигателями. Этот прибор больше предназначен для задач управления, чем для проведения вычислений.

Рис. 8.86. Однокристальный микропроцессор со схемами ввода/вывода.

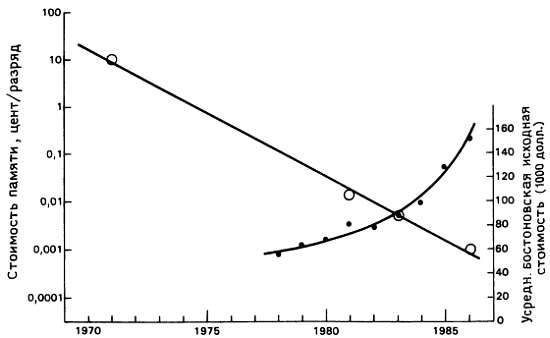

Революция в микропроцессорах не проходила в одиночестве, и мы видим удвоение компьютерной мощности и размера памяти (в настоящее время 1 Мбит, сравните с 16 Кбит на кристалле на время написания первого издания этой книги) каждый год, в то же время цены развиваются драматически (рис. 8.87). Наряду с укрупнением и улучшением процессоров и памяти, последние работы сверхскоростных приборов и больших параллельных архитектур обещают более волнующие события в последующие годы.

Рис. 8.87. Закон Кремниевой Долины: кривая обучения.

Более 800 000 книг и аудиокниг! 📚

Получи 2 месяца Литрес Подписки в подарок и наслаждайся неограниченным чтением

ПОЛУЧИТЬ ПОДАРОК