Микросхемы аппаратной поддержки микропроцессора

В нашем микропроцессорном приборе использованы 22 интегральные схемы, из которых 10 представляют собой мощные функциональные БИС (ЦП, память, параллельные и последовательные порты, календарь-часы, АЦП и ЦАП), а остальные 12, составляющие очевидное большинство, являются низменными вентилями, триггерами, буферами и фиксаторами. Эти микросхемы низкой и средней степени интеграции нужны для сочленения между собой больших микросхем и иногда называются «склеивающей логикой». Количество этого клея можно существенно уменьшить, если прибегнуть к помощи ПЛМ или даже (в условиях массового выпуска) заказных или полузаказных микросхем, специально разработанных под конкретную задачу. Тем не менее, фиксаторы и, особенно, тристабильные буферы используются весьма интенсивно во всех микропроцессорных системах, так что краткий обзор имеющихся возможностей вполне уместен. После этого мы коснемся некоторых распространенных поддерживающих БИС (последовательные и параллельные порты и преобразователи) и завершим главу обсуждением запоминающих устройств.

11.10. Микросхемы средней степени интеграции

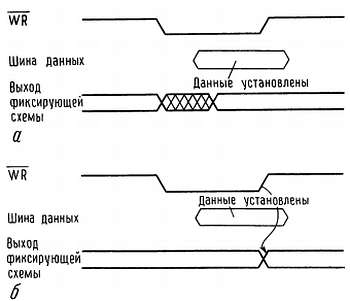

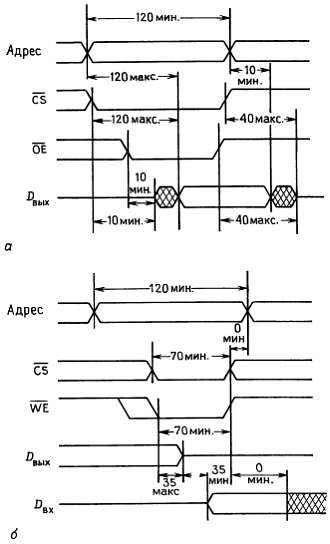

Фиксаторы и D-регистры. Фиксаторы и регистры уже упоминались в разд. 8.24. Термин «фиксатор», строго говоря, относится к прозрачному фиксатору, у которого состояние выходов повторяет состояние соответствующих входов (на время действия сигнала разрешения). Так называемый фиксатор с фиксацией по фронту является, в действительности, регистром D-типа. Он состоит из D-триггеров с общим тактовым входом. Различие в функционировании этих схем приводит к важным последствиям, когда они используются для фиксации данных, поступающих с магистрали, что связано с особенностями относительной синхронизации во времени сигналов данных и строба записи. В частности, в соответствии с протоколом некоторых микропроцессорных магистралей (например, машин IBM PC), данные не обязательно будут достоверными на фронте строба записи, однако гарантируется их достоверность на срезе этого сигнала (и в течение некоторого минимального времени после него); см. рис. 10.6 и 11.22. При использовании прозрачного фиксатора с разрешением на все время стробирующего сигнала на его выходе почти наверняка появятся переходные состояния, как это показано на рис. 11.22.

Рис. 11.22. Синхронизация цикла записи, а — прозрачный фиксатор; б — регистр с фиксацией по перепаду.

С другой стороны, выходы регистра D-типа (тактируемого в нашем случае по срезу строба) изменяют свое состояние по перепаду строба и гарантированно не будут иметь ложных состояний. Важно отметить, что выходные биты, состояние которых с момента последнего цикла записи не изменялось, будут неизменно находиться в тех же состояниях, не подвергаясь действию переходных процессов; таким образом, с помощью выходных линий фиксатора можно спокойно создавать сигналы данных и стробов для управления последующими электронными цепями.

Делая выбор между фиксатором и регистром, учтите, что на выходе прозрачного фиксатора достоверные данные появляются раньше, и иногда это может оказаться решающим доводом. Учтите также, что на многих магистралях (в частности, МП 68008) правильные данные поддерживаются в течение всего стробирующего сигнала с учетом времен упреждения и удержания, и в этом случае D-peгистр можно тактировать по фронту, если для этого хватит времени упреждения.

Естественно, что на такой магистрали прозрачные фиксаторы не будут иметь на выходах переходных состояний. На рынке имеется большое разнообразие и D-регистров, и прозрачных фиксаторов, с такими характерными чертами, как вход сброса, «разнесенные» выводы (все входы на одной стороне, все выходы на другой), инверсные выходы, тристабильные выходы (удобные для подключения к шине), а также раздельные по входам сигналы разрешения. Последнее качество упрощает внешнюю логику, позволяя тактировать фиксатор сигналом строба записи, а разрешать по входу сигналом с выхода дешифратора адреса. Характеристики фиксаторов были перечислены в табл. 8.9. Всеобщими любимцами являются восьмиразрядные тристабильные микросхемы `373 (фиксатор) `374 (D-регистр) или их модернизированные варианты с разнесенными выводами `573 и `574. Все они упакованы в DIP-корпусы с 20 выводами. В таком же корпусе выпускается микросхема `273, которая представляет собой микросхему `374 с сигналом сброса (но не тристабильную), а также микросхема `377-вариант `374 с сигналом разрешения (но без трех состояний). Более новые «долговязые» DIP-корпусы с 24 выводами имеют привычную ширину 0,3 дюйма, но предоставляют несколько дополнительных выводов. Так, новейшая серия `821 включает 8- и 9-разрядные регистры и фиксаторы со входами разрешения и сброса и тристабильными выходами, и все это в корпусах с разнесенными выводами.

Заметьте, что во многих приложениях некоторые из этих узких микросхем с 20 и 24 выводами могут оказаться удобнее причудливых БИС параллельных портов с 40 выводами (шириной 0,6 дюйма). Например, в нашей разработке мы использовали для ЭЛД-порта 8-разрядный регистр `273, а для порта DIP-переключателей 8-разрядный буфер `240. Вместо этого можно взять БИС параллельного порта вроде Zilog 8536 (хотя для такого примитивного прибора хватило бы и более простой микросхемы Intel 8255), которая стоит дороже, потребляет больше места и питания и требует дополнительного программирования. Однако для БИС характерна меньшая мощность выходов (1,7 мА на выходе и ничтожный входной ток у микросхемы 8255, в сравнении с 8 мА как на входе, так и на выходе у микросхемы `НСТ273). Некоторые микросхемы фиксаторов/регистров средней степени интеграции, когда дело доходит до выходных характеристик, напоминают могучих битюгов: микросхемы семейства `АС(Т) могут принимать и отдавать до 24 мА, а для серии `AS821 характерны значения 24 мА по входу и 48 мА по выходу. С другой стороны, БИС начинают играть всеми цветами радуги, когда вам требуется богатство возможностей (прерывания, причудливые режимы входов и выходов и т. д.), а не просто грубая сила.

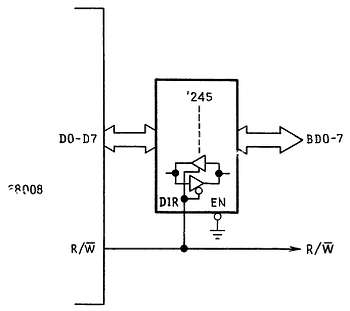

Буферы. Другой тип микросхем, используемый в микропроцессорных разработках целыми пригоршнями, — это тристабильные буферы. С их помощью на шине устанавливают адреса и данные. Чаще всего вы просто посылаете данные в ЦП, как это было с вашим простым вводом данных с DIP-переключателя. Как и в случае фиксаторов, имеются варианты микросхем шириной 8 бит и более, с 20 и 24 выводами. Микросхемы могут иметь такие черты, как входной гистерезис (для подавления шума), инверсные выходы, разнесенные выводы, а также раздельные входы разрешения для двунаправленной передачи. Специальные двунаправленные буферы со входами направления и разрешения (вместо пары входов разрешения) называются приемопередатчиками; в табл. 8.5 перечислены их характеристики.

На рис. 11.23 показан двунаправленный буфер, использованный для усиления относительно маломощной (~ 5 мА) шины данных микропроцессора, что позволяет нагружать ее сопротивлением и емкостью платы, заполненной микросхемами; такие буферы обязательны в микрокомпьютерах, где плата ЦП должна направлять относительно большие токи в системную шину на объединительной плате, характеризующуюся высокой емкостью.

Рис. 11.23. Шинный приемопередатчик.

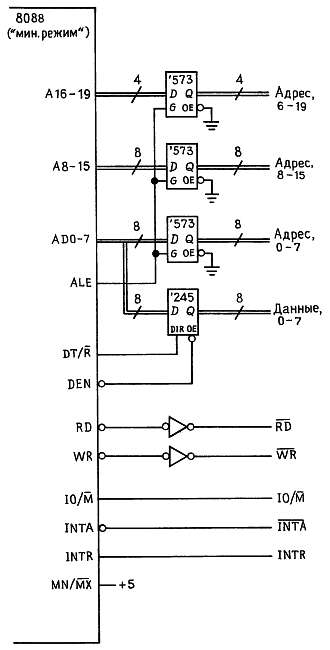

Часто можно найти микросхему средней степени интеграции с тристабильным выходным буфером и другими удобными для вас чертами; например, счетчик, фиксатор или даже АЦП/ЦАП с тристабильными выходами можно непосредственно подсоединить к микропроцессорной шине. В нашем примере так подключены АЦП//ЦАП. На рис. 11.24 показан другой пример буферизации шины: в некоторых микропроцессорах (например, 8086 и 8088) для экономии места функции выводов комбинируются, и на одни и те же выводы мультиплексируются и данные, и младшие разряды адреса.

Рис. 11.24. Мультиплектированная шина данных/адреса.

Выходной сигнал ALE (address latch enable, разрешение адресных фиксаторов) сопутствует правильному адресу и используется, как это показано на рисунке, для разрешения группы фиксаторов. Однако фиксировать данные нет необходимости, потому что стробирующие сигналы RD' и WR' действуют только когда сигналы данных имеют правильное значение. Обратите внимание на использование для буферизации двунаправленных линий данных приемопередатчика `245.

11.11. Периферийные БИС

Общие характеристики. Как уже упоминалось, БИС аппаратной поддержки микропроцессора обычно выполняются на базе КМОП- или nМОП- технологии и заключаются в корпуса с 28 или 40 выводами. Для таких БИС характерна высокая степень гибкости, причем их параметры часто допускают программную настройку. Обычно эти БИС предназначаются для определенных микропроцессоров, но фактически их универсальность позволяет использовать БИС одной фирмы с микропроцессором другой; так, мы объединили в нашей разработке календарь-часы фирмы Intersil и два порта фирмы Zilog с ЦП фирмы Motorola. Новые модели периферийных БИС обычно дороги (например, цена микросхемы 8530 составляет около 25 долл.), стоя иной раз больше, чем сам ЦП. Однако постепенно цена модели падает по экспоненциальному закону, что характерно для технологии интегральных схем (и, к сожалению, мало для чего еще в этом мире!). На рис. 8.87 был проиллюстрирован этот, видимо, универсальный закон «Кремниевой Долины» (расположенной на разломе Сан-Андреас между Сан-Франциско и Сан-Хосе).

Несмотря на наши иной раз нелестные замечания в адрес периферийных БИС, они в ряде случаев абсолютно незаменимы; достаточно вспомнить дисковые и видеоконтроллеры. Другим широко распространенным типом БИС поддержки является УСАПП, универсальный синхронно-асинхронный приемопередатчик.

Как использовать УСАПП. УСАПП представляет собой микросхему последовательного порта с микропроцессорным управлением, например Zilog 8530 в нашей разработке. Хороший УСАПП обеспечивает программное управление скоростью передачи, многообразие форматов кадра (число бит, контроль четности и проч.), универсальные синхронные режимы работы (по протоколам вроде HDLC и SDLC), выбор метода модуляции (без возвращения к нулю, частотный, манчестерский), восстановление тактовой синхронизации, контроль ошибок и т. д. Большинство УСАПП обеспечивает режим прерываний, а многие даже блочную передачу данных по каналу ПДП. Почти любое семейство ЦП имеет собственный УСАПП, хотя о совместимости разных УСАПП мало кто думает. Например, фирма IBM для работы с МП Intel 8088 на своих компьютерах PC выбрала УСАПП National 8250 вместо Intel 8251. Мы остановились на Zilog 8530 (он используется также в компьютере Макинтош) из-за его гибкости, доступности и цены, и именно с его помощью мы рассмотрим вопросы подключения и программирования УСАПП.

УСАПП чаще всего используются для пересылки данных на или из терминалов, модемов, устройств для получения твердых копий (принтеры, плоттеры), а также для непосредственной связи компьютеров в общем во всех случаях, когда основными требованиями являются универсальная совместимость и простота соединения. Обычно по линии с помощью биполярных уровней интерфейса RS-232 последовательно передаются коды ASCII, как это было описано в разд. 9.14 и 10.19. В таких простых системах связи УСАПП эксплуатируется в асинхронном режиме, когда каждый 8-битовый символ заключается между старт- и стоп-битами и передается в виде 10-битовой строки с одной из стандартных скоростей; для такого рода применений микросхема 8530 слишком хороша.

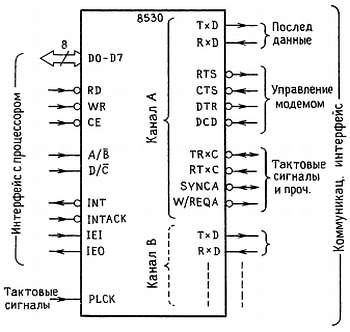

Микросхема 8530 выпускается в корпусе с 40 выводами (рис. 11.25); она взаимодействует с ЦП с помощью набора процессорных интерфейсных линий, а с внешним миром — одновременно и независимо с помощью набора коммуникационных интерфейсных линий.

Рис. 11.25. Сигналы «последовательного коммуникационного контроллера» (УСАПП) Zilog 8530.

Интерфейс с процессором. Для подключения к шине ЦП в микросхеме 8530 предусмотрены 8 двунаправленных линий данных, а для программно-управляемого ввода-вывода обычная пара стробирующих сигналов (RD', WR') и сигнал разрешения микросхемы (СЕ'). Вход А/В определяет, к какому из двух каналов УСАПП осуществляется обращение, а сигнал D/C' показывает, передаются ли данные (высокий уровень D/C') или информация управления/состояния (низкий уровень D/C').

Как и в микросхеме 8536, здесь предусмотрено большое количество регистров управления/состояния, доступ к которым осуществляется парами последовательных пересылок (посмотрите еще раз программные строки инициализации порта 8536). Обычно линии А/В и D/C' попросту подключаются к младшим адресным линиям ЦП, что отображает их на начало адресного пространства, начинающегося с базового адреса УСАПП (определяемого логикой декодирования адреса в устройстве). Наконец, интерфейс с процессором включает четыре линии прерываний.

Коммуникационный интерфейс. Каждый из двух каналов УСАПП (обозначаемых А и В) включает линии передачи и приема последовательных данных (TxD, RxD) вместе с линиями, обеспечивающими квитированное управление модемом (RTS, CTS и т. д.). Соответствующие этим линиям выводы можно обнаружить в разъеме на задней панели компьютера. Кроме этого, предусмотрены менее знакомые тактовые линии, используемые только для синхронной передачи (TRxC, RTxC). Наконец, УСАПП требуется внешний тактовый сигнал с частотой, в 32 раза превышающей наивысшую скорость передачи.

УСАПП не имеет никакого представления о биполярных уровнях интерфейса RS-232, поэтому на всех упомянутых линиях следует использовать драйверы и приемники уровней RS-232. В течение десятилетий в качестве интерфейсных микросхем для уровней RS-232 использовались классические модели биполярных счетверенных драйвера 1488 и приемника 1489; однако для нашего прибора мы выбрали КМОП-микросхему МАХ233 (сдвоенный драйвер/приемник), большим достоинством которой является наличие встроенных удвоителей напряжения и инверторов, что позволяет ограничиться единственным источником питания +5 В. Заметьте, что мы не связывались с линиями управления модемом (RTS, CTS, DSR, DTR); вообще их, как правило, игнорируют, используя вместо аппаратного программное квитирование (Ctrl-S, Ctrl-Q), включаемое в поток данных.

Программное обеспечение. Как уже отмечалось, режимы работы УСАПП устанавливаются командами программы. Байт, посылаемый в УСАПП в командном режиме (сигнал D/C' имеет низкий уровень), интерпретируется УСАПП, как команда управления и устанавливает рабочий режим. Таким образом можно определить вид передачи (синхронная или асинхронная), число стоп-бит, контроль четности или нечетности и т. д. Простые УСАПП вчерашнего дня имели всего один управляющий регистр и программировались легко; хитроумные микросхемы вроде 8530 содержат буквально десятки регистров и для программирования требуют квалификации доктора философии. К сожалению, такова цена, которую вы платите за исключительную гибкость мощных БИС аппаратной поддержки микропроцессора.

Для иллюстрации сказанного рассмотрим последовательность команд инициализации микросхемы 8530 для работы в следующем режиме: асинхронная последовательная передача по каналу А, скорость 1200 бод, 8 бит, без контроля четности, 1 стоп-бит; кроме того, мы запретим прерывания. Полная процедура инициализации длинна и утомительна; мы приведем программу целиком, однако во всей красе рассмотрим лишь один-два важнейших командных байта. В табл. 11.6 перечислены регистры записи и чтения микросхемы 8530, доступ к которым, как мы уже объясняли, осуществляется в два этапа: сначала передается номер регистра в качестве команды (D/C' в низком состоянии), а затем происходит запись в регистр (или чтение из него).

Таблица 11.6. Регистры микросхем Zilog 8530

Регистр · Функция

_____________________

Регистры чтения

RR0 · Состояние буферов приема-передачи и внешнее состояние

RR1 · Состояние условия специального приема

RR2 · Немодифицированный вектор прерывания (канал А); модифицированный вектор (канал В)

RR3 · Биты незавершенных прерываний

RR8 · Буфер приема

RR10 · Общее состояние

RR12 · Счетчик скорости пересылки (младший байт)

RR13 · Счетчик скорости пересылки (старший байт)

RR15 · Информация о прерывании, внешнее/состояние

Регистры записи

WR0 · Инициализация, указатели

WR1 · Прерывания и пересылка, определение режима

WR2 · Вектор прерывания

WR3 · Прием, параметры и управление

WR4 · Общие параметры и режимы

WR5 · Передача, параметры и управление

WR6 · Символы синхронизации или адресное поле SDLC

WR7 · Символ синхронизации или флаг SDLC

WR8 · Буфер передачи

WR9 · Управление и сброс прерывания ведущего

WR10 · Биты общего управления передачи/приема

WR11 · Управление режимом генератора

WR12 · Счетчик скорости пересылки (младший байт)

WR13 · Счетчик скорости пересылки (старший байт)

WR14 · Биты общего управления

WR15 · Управление прерыванием, внешнее/состояние

Для буферов передачи и приема (WR8 и RR8) двухэтапная процедура не приемлема, так как эти регистры используются при пересылке каждого байта; для них достаточно простых операций чтения или записи при D/C' в высоком состоянии. Точно так же, байт состояния буфера требует непосредственного доступа, поскольку чтение его флага обычно осуществляется при каждой пересылке байта данных; в микросхеме 8530 предусмотрено чтение RR0 с помощью простой операции чтения команды/состояния (D/C' в низком состоянии). Ниже мы рассмотрим все это подробнее на основе простых программ на языке ассемблера.

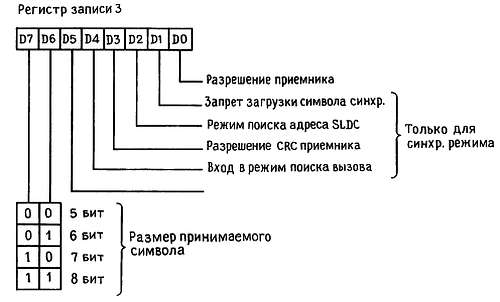

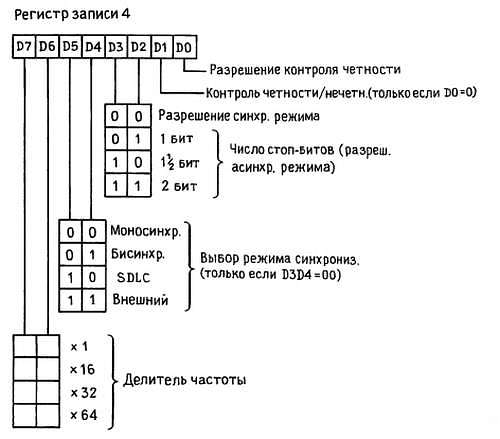

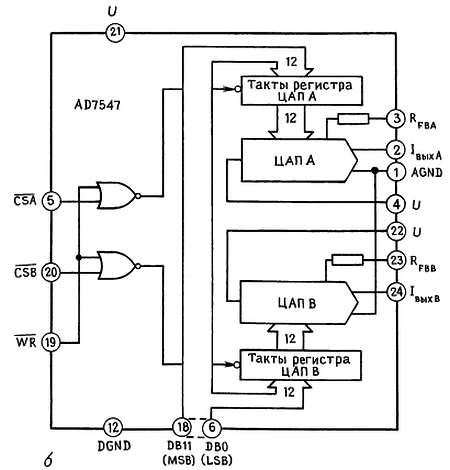

Каждый бит каждого регистра что-то означает. Например, на рис. 11.26 можно найти регистры WR3 и WR4, с помощью которых устанавливаются различные коммуникационные характеристики.

Рис. 11.26. Два регистра, используемые для инициализации микросхемы Zilog 8530.

В регистре WR3 к асинхронным операциям относятся только биты D0 разрешения приемника, D5 разрешения аппаратного квитирования (см. след. раздел) с помощью сигналов управления модемом CTS и DCD, а также два старших бита, определяющие число бит на символ. Остальные биты связаны с синхронными режимами, которые мы собираемся выключить соответствующим выбором D2-D3 в WR4. Таким образом, мы устанавливаем (D7, D6) = (1,1), D5 = 0 и D0 = 1, т. е. в WD3 мы посылаем шестнадцатеричный байт С1. С помощью WR4 мы задаем режим генератора x16 (минимальный делитель для асинхронных операций — УСАПП должен выполнять опрос сигнала каждого бита в его середине, поэтому частота входного генератора делается кратной частоте передачи), 1 стоп-бит на символ (используется всегда, за исключением устаревшего стандарта на телетайпную передачу со скоростью 110 бод), отсутствие контроля четности; получается шестнадцатеричный байт 44. Заметьте, что состояние битов D5-D4 не имеет значения, так как они управляют синхронной передачей; произвольно также состояние D1 (контроль четности или нечетности), если D0 (включение контроля) равен 0. Заметьте также, что установка 1 стоп-бита на символ (что имеет смысл только для асинхронного режима) автоматически выключает синхронный режим, а вместе с ним и все биты регистра управления, определяющие синхронные операции (например, D4-D1 в регистре WR3). Таким же образом можно управиться и с остальными управляющими регистрами. Это довольно скучная работа, в процессе которой легко допустить ошибки.

В табл. 11.7 приведены правильные, как мы надеемся, значения байтов (мы их тщательно проверили!).

Таблица 11.7. Инициализация последовательного порта 85301)

Регистр · Байт2) · Результат

________________________________

WR0 · (Указатель регистра) · Используется для доступа к WR1-WR15

WR1 · 00 · Запрет прерываний

WR2 · XX · Вектор прерываний (если разрешены)

WR3 · С1 · 8 бит, разрешение приема

WR4 · 44 · х15, 1 стоп-байт без контроля

WR5 · 68 · 8 бит, разрешение передачи

WR6 · XX · Символ синхронизации (только синхронный режим)

WR7 · XX · Символ синхронизации (только синхронный режим)

WR8 · (Буфер передачи) · Передаваемые данные (прямой доступ с D/C' = 1)

WR9 · СО · Сброс

WR10 · XX · Режимы синхронных операций

WR11 · 50 · Такты приема/передачи от генератора скорости пересылки

WR12 · 10210 · Делитель скорости пересылки - старший байт

WR13 · 00 · Делитель скорости пересылки - младший байт

WR14 · 03 · Разрешение генератора скорости пересылки

WR15 · XX · Режимы прерываний (если разрешены)

_____

1) Асинхронный режим, 1200 бод, 8 бит, без контроля четности.

2) XX-произвольное состояние; все числа шестнадцатеричные, кроме WR12.

Обратите внимание на состояние XX (произвольное) для регистров, игнорируемых нами, в силу того, что мы не используем ни прерываний, ни синхронного режима. Регистр WR9 выполняет полный сброс микросхемы, который должен предшествовать любым другим командам. С помощью регистров WR12 и WR13 устанавливается 16-разрядное значение делителя частоты передачи, которое для микросхемы 8530 дается выражением частота передачи = fтакт/[2 (режим генератора) x (делитель + 2)]. Таким образом, при частоте генератора 4 МГц и режиме генератор x16 для скорости передачи 1200 бод получаем делитель 10210 (фактически скорость передачи составит 1201,92 бод, что весьма близко к заданному значению). При выбранной нами частоте генератора возможны все стандартные скорости передачи вплоть до 9600 бод (для этой скорости делитель должен быть равен 13).

Заметьте, что в вашем распоряжении все многочисленные режимы работы УСАПП, устанавливаемые соответствующими последовательностями инициализирующих управляющих байт. Микросхема 8530, как и все УСАПП, обеспечивает также синхронную коммуникацию в различных режимах со скоростями до 1 Мбит/с; это особенно полезно для пересылки данных между двумя процессорами. Для нашего прибора такой способ пересылки не имеет смысла в силу ограниченного объема оперативной памяти, однако он может оказаться полезным при подключении жесткого диска.

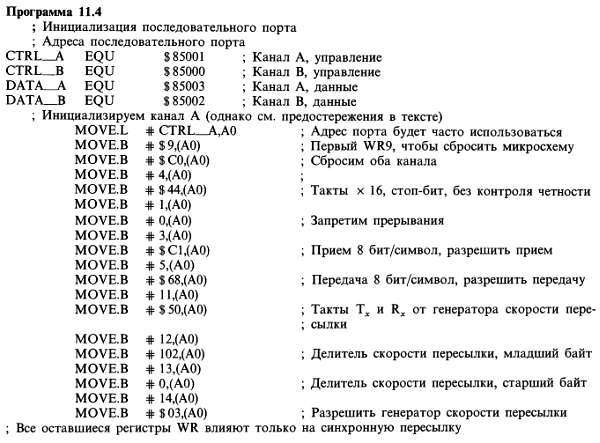

Обратите внимание на необходимость пересылки из ЦП в УСАПП правильной последовательности инициализирующих байт до того, как начнут передаваться какие-либо последовательные данные, как это было и в случае параллельного порта 8536; в нашем примере последовательный порт не использовался, так что мы опустили его инициализацию. Программа 11.4 дает понятие о процедуре инициализации. Сложность программы (включая декодирование таблиц с данными с целью определения управляющих байтов) — это цена, которую вы платите за исключительную гибкость БИС поддержки микропроцессора.

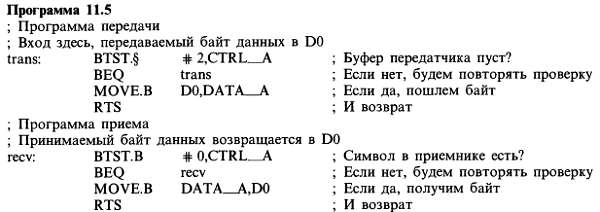

После того как с помощью управляющих регистров установлен режим работы УСАПП, можно передавать и принимать байты данных с помощью циклов ЦП записи и чтения при высоком уровне сигнала D/C'. С целью определения наличия нового, ожидающего приема в ЦП байта данных или возможности пересылки в УСАПП нового байта для его дальнейшей передачи следует опрашивать регистр состояния (при низком уровне D/C'), конкретно D0 в регистре RR0 в первом случае, и D2 в том же регистре во втором.

В дополнение к этому по другим битам регистра состояния можно судить о фиксации ошибки четности, потере принимаемых данных и т. д. Часто эти страшные удары судьбы можно игнорировать и смело идти вперед. В программе 11.5 приведены фрагменты пересылки данных при том же, что и раньше, отображении регистров на адресное пространство.

Учтите, что эти примеры, в которых используется программный ввод-вывод с проверкой состояния (см. разд. 10.06–10.08), иллюстрируют работу простейших программных драйверов. В них работа ЦП останавливается на время циклического опроса флага состояния. Использование механизма прерываний позволяет повысить эффективность работы ЦП; это особенно справедливо для операций ввода. Микросхема 8530 может возбуждать прерывания по любому указанному условию; от нее даже можно получить в качестве подтверждения выбранный вами 8-битовый вектор, если использовать линии подтверждения прерывания (IEI, IEO, INTACK). Все эти возможности реализуются с помощью управляющих байтов инициализации.

Микросхемы параллельного ввода-вывода (PIO). В состав нашего микропроцессорного прибора была включена многофункциональная микросхема параллельного порта (такого рода схемы часто объединяются с одним или несколькими таймерами). Использованная нами микросхема 8536 принадлежит тому же семейству, что и микросхема последовательного порта 8530 и использует схожие интерфейс с процессором и протокол настройки. Хорошие микросхемы параллельных портов позволяют программировать для каждого бита в отдельности направление передачи и режим (с фиксацией, с открытым стоком, с инверсией). Протокол передачи данных также можно запрограммировать; например, в микросхеме 8536 можно разрешить векторизуемые прерывания по любому сочетанию входных бит. Можно также выбрать один из четырех режимов квитирования (см. ниже).

Микросхемы РIO, как и все периферийные БИС, разрабатываются на базе nМОП- и КМОП-технологий, причем в новых разработках используется в основном последняя. С выходов таких схем можно снять, как правило, несколько мА, однако nМОП-схемы, в отличие от КМОП, обеспечивают лишь доли мА. Поэтому они обычно используются совместно с микросхемами мощных драйверов, позволяющих подключать к ним нагрузку, требующую значительных токов. Не пытайтесь подключать реле непосредственно к выходу микросхемы РIO (см. наши замечания относительно микросхем среднего уровня интеграции в разделе «Фиксаторы и D-регистры»).

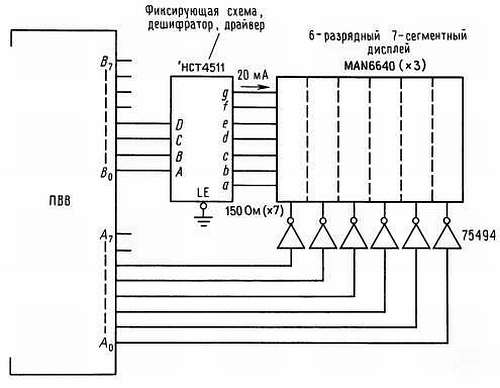

На рис. 11.27 показан пример реальной схемы, конкретно для управления 6-разрядным дисплеем.

Рис. 11.27. Управление мультиплексированным дисплеем от РIO.

Конечно, вам придется написать программу для периодического вывода последовательных десятичных чисел, а также и «шагающего бита» через порт А, не забыв запретить прерывания на время вывода, чтобы предотвратить мерцание. Другой, более простой способ управления многоразрядным ЭЛД-дисплеем в микропроцессорной системе заключается в использовании чего-то вроде семейства «интеллектуальных дисплеев» фирмы Siemens-дисплейных секций, отображаемых на память, и выглядящих с точки зрения ЦП просто как участки памяти (см. рис. 9.24); поскольку такие дисплеи запоминают выводимые числа, запись в них требуется выполнять только при смене отображаемого числа.

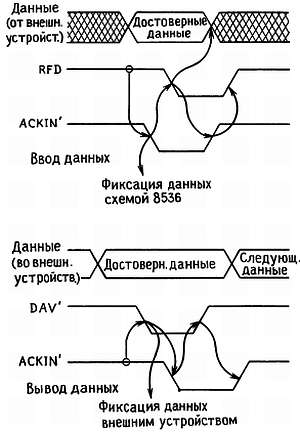

Квитирование. Процедура квитирования требует некоторых пояснений. Представьте себя на месте внешнего устройства, посылающего байты данных в процессор через порт РIO. Вы хотите узнать, готов ли РIO принять следующий байт, т. е. извлечен ли процессором предыдущий байт. Для выполнения этой операции следует предусмотреть в РIO специальный выход «готов к приему данных» (ready for data, RFD), который сбрасывается РIO после получения от вас нового байта, и вновь устанавливается после того, как этот байт забирается центральным процессором. Другими словами, вы имеете право стробировать свои данные в любой момент, если только установлен RFD.

На рис. 11.28 показано, как реализуется это «взаимное квитирование», которое является одним из четырех режимов квитирования, предусмотренных в микросхеме 8536.

Рис. 11.28. Квитирование.

При вводе данных внешний источник может установить данные, но не устанавливает строб ACKIN' (такое название этого вывода придумала фирма Zilog!) до обнаружения установленного сигнала RFD. Устройство снимает строб (и может снять данные), обнаружив сброс RFD, затем снова ожидает установки RFD. При выводе данных процессы протекают аналогично. РIO устанавливает сначала данные, затем сигнал DAV' (data available, данные установлены). Внешнее устройство фиксирует данные, после чего устанавливает сигнал подтверждения ACKIN'. Это заставляет РIO сбросить и данные, и DAV'. Последнее воспринимается внешним устройством, как команда на сброс ACKIN', чем начинается новый цикл. Заметьте, что квитирование полностью взаимно, т. е. каждый участник передачи данных на каждом шаге ждет вершения своей части операции вторым соучастником. Такое полностью взаимное квитирование гарантирует отсутствие потерь данных. Иногда, однако, протокол можно упростить. В микросхеме 8536 предусмотрен режим «импульсного квитирования», в котором сигнал ACKIN' не обязан ожидать разрешения на сброс; в этом случае сигнал ACKIN' представляет собой импульс длительностью по меньшей мере 250 нc, возбуждаемый, когда установлены RFD или DAV', как было описано выше.

Легко сообразить, что режим квитирования выбирается в процессе инициализации посылкой тех же всеобъемлющих управляющих байтов. Если выбран один из режимов квитирования, все или некоторые из четырех линий порта С используются в качестве ACKIN', DAV' и RFD. Если вы не назначаете порту режим квитирования, линии порта С можно использовать, как обычные биты ввода-вывода, точно так же, как порты А и В.

Предупреждение: общий недостаток многих периферийных БИС, особенно с тактирующим входом, заключается в непомерно большом времени успокоения после каждой операции. Весьма показателен наш опыт работы с микросхемой 8530: при использовании МП 68000 на частоте 10 МГц пришлось между последовательными циклами вывода включить несколько команд NOP, потому что скорость, с которой ЦП мог посылать последовательные байты (интервал между байтами 0,8 мкc) была выше скорости их приема микросхемой 8530 (минимальное значение «допустимого времени восстановления после доступа» для 8530 составляет 1,7 мкс). Учтите также своеобразные требования к синхронизации процессорного интерфейса. Вспомним, что в нашем микропроцессорном приборе периферийные схемы Zilog требовали необычно большого времени предустановки адреса по отношению к фронту строба чтения (80 не), что заставило нас добавить схемы для генерации задержанного сигнала RD'. Эти особенности, с которыми вы не встретитесь при использовании простых цифровых схем среднего уровня интеграции, являются результатом необходимости тактирования внутренних состояний микросхемы, относительно низкой скорости работы КМОП-схем, или и того, и другого.

Единственный путь борьбы с этими неприятностями БИС-тщательное проектирование, что включает в себя внимательное изучение технических характеристик микросхем, обмен опытом с другими пользователями и исчерпывающее тестирование. Если, испытывая опытный образец, вы замечаете какую-то аномалию, не надейтесь, что она пропадет в более тщательно разработанном конечном варианте. Как раз наоборот, именно аномалии вам и надлежит отыскивать. Обычно, отлаживая опытный образец, вы можете испытать свою схему гораздо надежнее, искусственно изменяя тактовую частоту, питающее напряжение и, возможно, температуру (с помощью тепловой пушки).

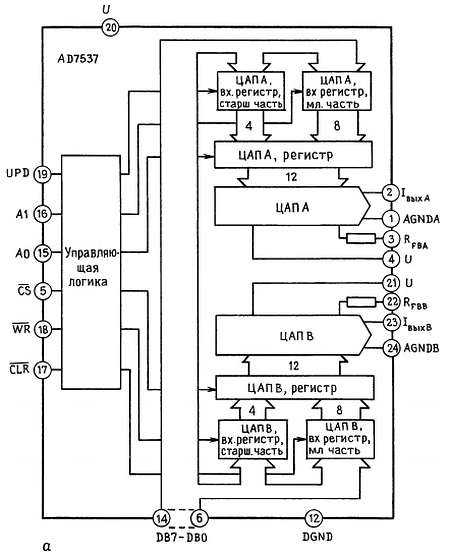

Аналого-цифровые и цифро-аналоговые преобразователи на микропроцессорной магистрали. Ввиду широкого внедрения устройств сбора данных с микропроцессорным управлением (в противоположность автономным приборам) новейшие модели АЦП и ЦАП стали разрабатываться с учетом возможности их подключения к микропроцессорной магистрали. Например, «микропроцессорно-совместимые» ЦАП имеют шины передачи входных данных шириной 1 байт и два входных буфера, так что вы можете зафиксировать 12-разрядную величину, поступающую по 8-разрядной шине, за два цикла записи; двойная буферизация обеспечивает одновременное поступление на вход преобразователя всех 12 разрядов преобразуемой величины, что уменьшает переходные выбросы на выходе. Аналогично этому микропроцессорно-совместимые АЦП комплектуются тристабильными выходными драйверами, организованными в группы шириной 8 бит. И АЦП, и ЦАП часто используют «магистрально-ориентированные» сигналы типа RD', WR' и CS'. Такие преобразователи можно непосредственно подключать к микропроцессорной магистрали, используя лишь незначительный объем «склеивающей» логики для декодирования адреса. Вам не приходится мучиться с обычными интерфейсными атрибутами вроде внешних фиксаторов и тристабильных драйверов. Можете вспомнить, как все просто выглядело в нашем приборе, включавшим и АЦП, и ЦАП.

Несколько примеров. Микросхема AD7537 фирмы Analog Devices представляет собой двухканальный 12-разрядный ЦАП с 8-битовой загрузкой (т. е. каждая 12-битовая величина загружается за два цикла магистрали, как 8 + 4), со средствами одновременного обновления двух 12-разрядных каналов с двойной буферизацией (рис. 11.29); вариант AD7547 снабжен входом, шириной 12 бит, предназначенным для 16-разрядных магистралей. Микросхема AD7572 той же фирмы — это 12-разрядный АЦП, не требующий «склеивающих» схем, с возможностью параллельного вывода шириной 8 или 12 бит через тристабильные драйверы; эту схему можно легко подключить к микропроцессорным магистралям шириной как 8, так и 16 бит. Некоторые преобразователи, совместимые с магистралями, даже позволяют задавать выравнивание слова, меньшего по ширине, чем магистраль, влево или вправо. Выбирая преобразователь для подключения к микропроцессорной магистрали, остерегайтесь устройств с замедленной синхронизацией процессорного интерфейса (что не имеет никакого отношения к скорости преобразования), которая может заставить вас предусматривать состояния ожидания, задержанные стробы и т. д. Например, микросхема AD558, во всех остальных отношениях превосходный автономный 8-разрядный АЦП, характеризуется минимальным временем упреждения данных по отношению к срезу сигнала WR' 200 нc, что требует, при использовании его с МП 68008, введения состояния ожидания.

Рис. 11.29. 12-разрядные двухканальные ЦАП (с любезного разрешения Analog Devices), а — микросхема 7537 с шириной загрузки 1 байт; б — микросхема 7547 с шириной загрузки 12 бит.

При подключении к микропроцессору любого АЦП с разрешением 12 бит и более подумайте об изоляции выходов микросхемы АЦП от системной магистрали с помощью буферов (или даже опторазвязок); в противном случае переходные процессы в цифровых цепях и наводки от микропроцессора могут легко ухудшить разрешение. При высоком разрешении (16 бит и более) может оказаться необходимым разместить преобразователь вне корпуса, содержащего цифровую электронику. В качестве примера возможных неприятностей мы можем описать наш опыт работы с промышленной платой 16-разрядного АЦП, предназначенного для IBM PC. Модуль преобразователя размещался прямо на плате, внутри компьютера. Мы скептически отнеслись к возможности достижения максимального 16-битового разрешения, и перед покупкой платы осведомились, какова будет реакция АЦП на приложение к его аналоговым входам постоянного напряжения. В отделе технической поддержки фирмы-изготовителя нас заверили, что колебания будут «не более двух соседних цифровых кодов». Фактически выходные показания метались в пределах семи соседних кодов, что снижало разрешение до 14 бит. По предложению фирмы мы принесли им плату для испытаний, которые лишь подтвердили проблему шума. Когда мы спросили «как же так?», нам сказали, что введший вас в заблуждение сотрудник уже у них не работает. Нам сообщили, что все их платы работают точно так же; и, добавляя оскорбления к ущербу, пригрозили взыскать с нас стоимость «обслуживания», состоявшего в испытаниях платы.

11.12. Запоминающие устройства

В обычном микрокомпьютере увеличить объем памяти несложно - вам лишь надо решить, сколько мегабайт стоит добавить, и к какому поставщику обратиться. Больше умственных усилий надо затратить при разработке прибора с микропроцессорным управлением, где распределение памяти является элементом проектирования, и где совместно используются блоки запоминающих устройств разных типов — энергонезависимые ПЗУ для хранения программ, а энергозависимые ОЗУ для временного размещения данных и стеков, а также как рабочее пространство программы. Энергонезависимые ПЗУ с «зашитыми» программами широко используются в микропроцессорных устройствах, чтобы избавиться от необходимости каждый раз при включении прибора загружать программу. В настоящем разделе мы рассмотрим различные виды памяти: статические и динамические ОЗУ (оперативные запоминающие устройства), РПЗУ (репрограммируемые постоянные запоминающие устройства), ЭРПЗУ (электрически стираемые репрограммируемые постоянные запоминающие устройства). Как только вы немного в них разберетесь, выбор уже не составит труда. Можете сразу обратиться к рис. 11.35, где мы свели воедино типы запоминающих устройств.

Статические и динамические ОЗУ. В статических ОЗУ биты хранятся в матрицах триггеров, в то время как в динамических ОЗУ-в заряженных конденсаторах. Бит, записанный в статическое ОЗУ, остается в нем до тех пор, пока не будет перезаписан, или пока не выключится источник питания. В динамическом ОЗУ данные, если их не «регенерировать», исчезнут менее чем через секунду. Другими словами, динамическое ОЗУ непрерывно забывает данные, и чтобы их сохранить, приходится периодически опрашивать «строки» двумерной матрицы битов в микросхеме памяти. Например, в ОЗУ объемом 256 кбит к каждому из 256 рядов приходится обращаться каждые 4 мс.

Вы можете задаться вопросом, кому же придет в голову выбирать динамическое ОЗУ? Дело в том, что обходясь без триггеров, динамическое ОЗУ занимает меньше места, в результате чего микросхема большей емкости оказывается дешевле. Например, популярное сегодня статическое ОЗУ емкостью 32Кх8 (256 кбит) стоит около 10 долл., в два раза больше нынешней цены динамического ОЗУ емкостью 1 Мбит. В результате, используя динамические ОЗУ, вы за половину стоимости будете иметь в 4 раза больше памяти.

Теперь, наверное, вы удивляетесь, кому же нужны статические ОЗУ (что-то вас кидает из стороны в сторону)? Основное достоинство статических ОЗУ заключается в их простоте. Отпадает необходимость в циклах регенерации, не нужно заботиться об их синхронизации (циклы регенерации конкурируют с обычными циклами обращения к памяти и должны поэтому жестко синхронизоваться). В простых системах с ограниченным числом микросхем памяти естественно использовать статические ОЗУ. К тому же большая часть нынешних статических ОЗУ используют КМОП-технологию, что существенно для приборов с батарейным питанием. Между прочим, статическое КМОП ОЗУ, автоматически переключаемое на батарейное питание при выключении основного (с помощью микросхемы управления питанием типа МАХ690), представляет неплохую альтернативу ПЗУ в качестве энергонезависимой памяти. Другим достоинством статических ОЗУ является их высокое быстродействие (выпускаются микросхемы с характерным временем 25 нc и менее), а также удобная компоновка секциями по 8 бит. Рассмотрим оба типа ОЗУ подетальнее.

Статические ОЗУ. Мы уже столкнулись со статическим ОЗУ в нашей микропроцессорной разработке, где одно такое ОЗУ емкостью 32Кх8 использовалось для размещения данных, стека и рабочей области (программа была записана в РПЗУ). Организовать обмен данными со статическим ОЗУ проще простого: в цикле чтения вы устанавливаете сигналы адреса, выбора микросхемы (CS') и разрешения выхода (OE'); запрошенные данные появляются на тристабильных линиях данных спустя максимум taa (адресное время доступа). В цикле записи вы устанавливаете сигналы адреса, данных и CS', а затем (спустя время упреждения адреса tas) импульс разрешения записи (WE'); достоверные данные записываются в конце импульса WE'. Действующие временные ограничения для 120 нс статического ОЗУ показаны на рис. 11.30, из которого видно, что «быстродействие» памяти — это время от установки достоверного адреса до достоверных данных (при чтении) или до завершения цикла записи (при записи). Для статических ОЗУ интервал времени между последовательными обращениями к памяти («длительность цикла») равен времени доступа; для динамических ОЗУ, как будет показано ниже, это не так.

Рис. 11.30. Синхронизация статического ОЗУ с быстродействием 120 нc. а — цикл чтения, б — цикл записи.

Микросхемы статических ОЗУ могут иметь емкость от 1 Кбит (или меньше) до 1 Мбит при ширине 1, 4 или 8 бит. Быстродействие (время доступа) колеблется от 150 до 10 нc или около того. В настоящее время широко используются недорогие статические КМОП ОЗУ емкостью 8Кx8 и 32Кx8 с временем доступа 80 нc, а также меньше по емкости, но более быстродействующие (< 3 нc) статические КМОП ОЗУ для кеш-памяти. Варианты микросхем могут иметь отдельные выводы для входов и выходов, два порта доступа и то или иное внешнее оформление (например, однорядный корпус SIP). Может быть это и существенно, однако заметьте, что вам не надо заботиться, чтобы линии данных ЦП подключались обязательно к одноименным выводам микросхемы памяти — ведь независимо от порядка соединения вы при чтении всегда получите то же, что записали! Это замечание справедливо и для адресов. Однако не пытайтесь так поступить с ПЗУ.

Упражнение 11.18. А почему?

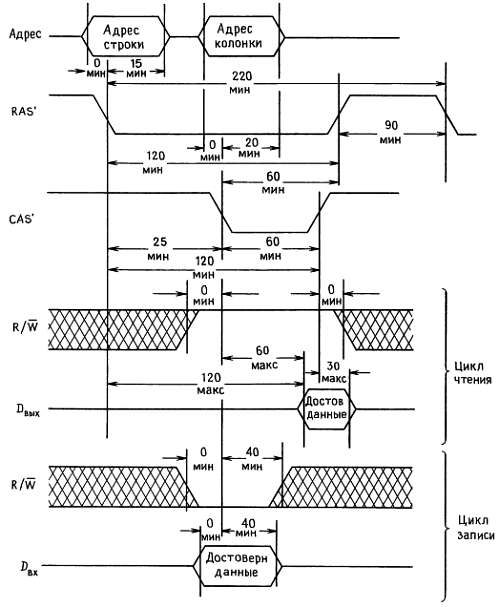

Динамические ОЗУ. По сравнению со статическими ОЗУ динамические ОЗУ — это сплошная мигрень. На рис. 11.31 показан нормальный цикл. Адрес (содержащий, например, для ОЗУ объемом 1 Мбайт 20 бит) расщепляется на две группы и мультиплексируется на вдвое меньшее число выводов, сначала «адрес строки», стробируемый сигналом RAS' (Row Address Strobe — строб адреса строки), а затем «адрес колонки», стробируемый сигналом CAS' (Column Address Strobe — строб адреса колонки).

Рис. 11.31. Циклы чтения и записи динамического ОЗУ (Motorola, 120 нc).

Данные записываются (или читаются в соответствии с состоянием входа направления R/W') вслед за установкой CAS'. Перед началом следующего цикла памяти должно пройти некоторое время «выдержки RAS», поэтому длительность цикла больше времени доступа; например, динамическое ОЗУ может иметь время доступа 100 нc и длительность цикла 200 нc. Цикл регенерации выглядит так же, но без сигнала СAS'. Вообще-то обычные обращения к памяти отлично ее регенерируют, если только вы можете гарантировать обращения со всеми возможными адресами строк!

Динамические ОЗУ, как и статические, выпускаются с шириной данных 1, 4 и 8 бит, емкостью от 64 Кбит до 4 Мбит и с быстродействием приблизительно от 70 до 150 нc. Наиболее популярны большие 1-битовые микросхемы, что вполне объяснимо: если вам нужна большая матрица памяти, скажем объемом 4 Мбайт и шириной 16 бит, и имеются в наличии ОЗУ емкостью 1 Мбит с организацией 1Мx1 и 128Кx8, имеет смысл использовать 1-битовые микросхемы, потому что (а) каждая линия данных будет подключена только к двум микросхемам (а не к 16), что существенно уменьшит емкостную нагрузку, и (б) эти микросхемы занимают меньше места, потому что меньшее число выводов данных более чем компенсирует дополнительные адресные выводы. Кроме того, 1-битовые микросхемы, как правило, дешевле. Приведенные рассуждения справедливы, если вы строите большую память, и не относятся, например, к нашему простому микропроцессору с памятью 32Кx8. Заметьте, однако, что улучшенная технология упаковки микросхем с высокой плотностью ("ZIP" и "SIMM") уменьшает важность минимизации числа выводов.

Существует ряд способов генерации последовательности мультиплексированных адресов и сигналов RAS, CAS и R/W', требуемой для управления динамическим ОЗУ. Поскольку это ОЗУ всегда подключается к микропроцессорной магистрали, вы начинаете работу с ним, обнаружив сигнал AS' (или эквивалентный ему), говорящий о том, что установлен правильный адрес из пространства динамического ОЗУ (о чем свидетельствуют старшие адресные линии). Традиционный метод заключается в использовании дискретных компонент средней степени интеграции для мультиплексирования адреса (несколько 2-канальных 2-входовых мультиплексоров `257) и генерации сигналов RAS, CAS, а также сигналов управления мультиплексором. Требуемая последовательность создается с помощью сдвигового регистра, тактируемого с частотой, кратной тактовой частоте микропроцессора или, что лучше, с помощью линии задержки с отводами. Для организации периодических циклов регенерации (только RAS) вам потребуется еще несколько логических схем и счетчик, отсчитывающий последовательные адреса строк. На все это уйдет около 10 корпусов.

Привлекательным способом, альтернативным «дискретным» схемам управления динамическим ОЗУ, является использование ПЛМ, причем для генерации всех необходимых сигналов достаточно одной-двух микросхем. Еще проще взять специальную микросхему «поддержки динамического ОЗУ», например, АМ2968. Такого рода микросхемы берут на себя не только мультиплексирование адресов и образование сигналов RAS/CAS, но также и арбитрацию регенерации вместе с образованием адресов строк; более того, они даже включают мощные драйверы и демпфирующие резисторы, которые нужны для подключения больших матриц микросхем памяти, как это будет объяснено ниже. К таким контроллерам динамических ОЗУ обычно прилагаются дополнительные микросхемы для синхронизации, а также обнаружения и коррекции ошибок; в результате небольшой набор микросхем полностью решает проблему включения динамического ОЗУ в вашу разработку.

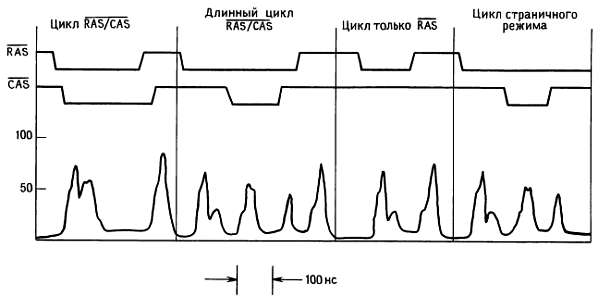

Впрочем, почти полностью! Основные неприятности с динамическими ОЗУ начинаются, когда вы пытаетесь освободиться от наводок на всех этих стробирующих и адресных магистральных линиях. Суть проблемы заключается в том, что несколько десятков корпусов МОП-схем оказываются разбросанными на большой площади системной платы, причем ко всем корпусам подходят управляющие и адресные шины. Для подключения к ним нескольких десятков микросхем требуются мощные выходные каскады Шоттки; однако большая длина линий и распределенная входная емкость в сочетании с крутыми фронтами выходных каскадов приводят к появлению «звона» большой амплитуды. Часто можно увидеть на адресных линиях ОЗУ отрицательные выбросы до —2 В! Типичным средством борьбы (не всегда полностью успешной) является включение на выходе каждого драйвера последовательных демпфирующих резисторов с сопротивлением около 33 Ом.

Другая проблема заключается в огромных переходных токах, часто достигающих величины 100 мА на линию. Представьте себе микросхему 8-разрядного драйвера, у которого большинство выходов случайно переключаются в одном направлении, например, с высокого уровня на низкий. Это приводит к переходному току величиной около 1 А, который на некоторое время повышает потенциал нулевого вывода, а вместе с ним и всех выходов, которые должны были иметь низкий уровень. Отмеченная проблема отнюдь не носит академического характера — однажды мы наблюдали сбои в работе памяти как раз из-за таких переходных токов на нулевом выводе, образующихся из-за выбросов токов CAS-драйвера. При этом наводки, проходящие в RAS-драйверы той же микросхемы, оказывались достаточными для завершения цикла памяти!

Дополнительным источником наводок в динамических ОЗУ являются большие переходные токи, образованные микросхемами в целом, причем наиболее честные разработчики даже включают сведения об этом явлении в свои технические материалы (рис. 11.32).

Рис. 11.32. Переходные токи динамического ОЗУ.

Обычным средством борьбы является установка шунтирующих конденсаторов, подключенных к нулевой линии с малой индуктивностью; считается разумным шунтировать каждую микросхему керамическим конденсатором с емкостью 0,1 мкФ. Мы пришли к выводу, что логические драйверы 74F с внешними резисторами хорошо работают с динамическим ОЗУ, как и специальные драйверы типа Аm2966, которые включают интегральные демпфирующие резисторы. Контроллер динамического ОЗУ Аm2968, упоминавшийся выше, по заверениям разработчиков может обслуживать до 88 микросхем памяти без внешних компонент, давая при этом отрицательные выбросы не более —0,5 В. Даже более важным, нежели выбор конкретного драйвера, является использование нулевых линий с низкой индуктивностью и частого шунтирования U+. Двухсторонние платы с узкими линиями заземления неминуемо приведут к неприятностям; макетные платы с накруткой проводов обычно немногим лучше.

Важно понимать, что сбои памяти, возникающие из-за наводок, могут в сильной степени зависеть от распределения бит в передаваемых данных и не всегда проявляются в простых тестах памяти на чтение/запись. Лучшим способом обеспечить надежную работу памяти является консервативное проектирование и исчерпывающее тестирование памяти (с осциллографическим исследованием форм сигналов).

Постоянные запоминающие устройства (ПЗУ). ПЗУ относятся к памяти, неразрушаемой при выключении питания (энергонезависимой), и нужда в них возникает практически в любой компьютерной системе. К примеру, в микрокомпьютерах необходимо иметь по крайней мере небольшое ПЗУ для хранения последовательности команд начальной загрузки, которая включает не только строки выделения стека и инициализации портов и прерываний, но также и команды, обеспечивающие чтение операционной системы с диска. Когда ваш персональный компьютер выполняет тестирование памяти и затем загружает DOS, он выполняет приказы некоторого ПЗУ. Кроме того, для микрокомпьютера типично хранение в ПЗУ некоторой части операционной системы (обычно наиболее аппаратно-зависимых модулей); эта часть называется «базовой системой ввода-вывода» (basic I/O system, BIOS) и обеспечивает стандартный механизм для обращения операционной системы к конкретным портам.

ПЗУ широко используются для хранения различных таблиц, например, для генератора символов, отображаемых на экране дисплея. В предельном случае вообще вся операционная система, включая даже компиляторы и графические программы, может размещаться в ПЗУ. Например, в микрокомпьютере Macintosh значительная часть системного программного обеспечения записана в ПЗУ, и почти все 256 Кбайт ОЗУ отдаются пользователю. Однако такой «ПЗУ-ориентированный» подход используется в микрокомпьютерах относительно редко ввиду его негибкости; заметьте, однако, что исправление ошибок и умеренные усовершенствования программного обеспечения могут осуществляться с помощью заплат, размещаемых в ОЗУ.

В приборах с микропроцессорным управлением ПЗУ используются более широко. В ПЗУ хранится вся автономная программа, а энергозависимое ОЗУ используется только для хранения массивов и временных данных. Именно так было сделано в нашем усреднителе сигналов. ПЗУ часто оказываются полезными в дискретной цифровой аппаратуре, например, для конструирования произвольных конечных автоматов, или в качестве хранилища таблиц поправок для линеаризации функции отклика измерительной системы. Рассмотрим кратко разные виды энергонезависимой памяти: ПЗУ с масочным программированием, а также электрически стираемые ЭРПЗУ.

РПЗУ. Стираемые программируемые постоянные запоминающие устройства выполняются в виде больших микросхем с кварцевым окном. Это, несомненно, самый популярный тип энергонезависимой памяти для компьютеров. РПЗУ используют КМОП- и МОП-технологию и состоят из больших матриц полевых и МОП-транзисторов с плавающим затвором, которые можно зарядить с помощью «лавинной инжекции» — процесса пробоя слоя, изолирующего затвор, при приложении напряжения свыше 20 В. Данные хранятся в РПЗУ неограниченно долго в виде ничтожного заряда (около 106 электронов) изолированных «погребенных» затворов, которые можно рассматривать как конденсаторы с постоянной времени порядка столетий. Чтобы прочитать состояние отдельного конденсатора, ему надо выступить в качестве затвора канала полевого МОП-транзистора. Поскольку затвор электрически недоступен, стереть заряд можно лишь облучая микросхему интенсивным потоком ультрафиолетовых лучей в течение 10–30 мин, отчего запасенный заряд стекает за счет явления фотопроводимости. В результате отдельные байты РПЗУ выборочно стереть нельзя.

В первом издании этой книги мы упоминали «классическую» микросхему 2716, РПЗУ 2Кx8, стоившую 25 долл. Теперь она стала такой классической, что ее уже нигде не достанешь! Типичные РПЗУ нашего времени имеют емкость от 8Кx8 до 128Кx8 и цену несколько долларов. Время доступа обычно составляет 150–300 нc, хотя такие компании, как Cypress, предлагают ПЗУ небольшого объема с быстродействием 25 нc. Чтобы запрограммировать РПЗУ, к нему надо просто приложить повышенное напряжение (обычно 12,5 или 21 В), устанавливая при этом требуемые значения байтов.

Исходные алгоритмы требовали 50 мс на программирование каждого байта (что дает 100 с для микросхемы 2716, но для РПЗУ умеренного объема 32Кx8 превращается в полчаса). Выпуск больших ПЗУ потребовал от разработчиков изобретения более совершенных алгоритмов, в которых каждый байт программируется последовательностью импульсов длительностью 1 мс, причем после каждой записи делается попытка чтения; когда байт считывается правильно, выполняется окончательная запись, равная по длительности утроенной сумме всех предыдущих. Большая часть байтов программируется первым же импульсом, в результате на каждый байт тратится около 4 мс, а на все ПЗУ объемом 32Кx8 — 2 мин.

РПЗУ очень удобны при разработке опытных образцов, так как после стирания их можно использовать повторно. Они также применяются при выпуске небольших партий приборов. В продаже имеются более дешевые варианты РПЗУ без кварцевого окна, иногда называемые «РПЗУ однократного программирования». Хотя эти микросхемы не следовало бы называть РПЗУ, инженеры не желают изменять привычное название. Консервативные производители РПЗУ гарантируют сохранение в них информации в течение лишь 10 лет. Эта величина предполагает наихудшие условия (в частности, высокую температуру, которая приводит к утечке заряда); в действительности РПЗУ, похоже, не теряют данные, если только вам не попалась дефектная партия.

Для РПЗУ характерно ограниченное число циклов репрограммирования, т. е. стирания и программирования заново. Производители неохотно называют это число, хотя вы можете считать, что микросхема заметно ухудшит свои характеристики лишь после 100 или около того циклов стирания / программирования.

Масочные ПЗУ и ПЗУ с плавкими перемычками. Масочно-программируемые ПЗУ относятся к категории заказных микросхем, которые рождаются с указанным вами расположением бит. Фирма-производитель преобразует вашу спецификацию бит в маску металлизации, используемую далее при изготовлении ПЗУ. Такая процедура хороша для больших партий микросхем, и вам, надеемся, не придет в голову заказывать ПЗУ с масочным программированием для макетного образца. Типичная стоимость составляет от 1 до 3 тыс. долл. за производственный цикл, и фирмы неохотно берут заказы на партии ПЗУ менее тысячи штук. При таких количествах микросхема может обойтись в несколько долларов.

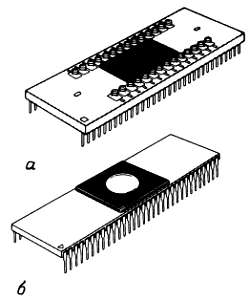

Многие однокристальные микроконтроллеры содержат в том же корпусе несколько кбайт ПЗУ и ОЗУ, так что законченный прибор может обходиться без дополнительных микросхем памяти. В большинстве случаев микроконтроллерное семейство включает варианты, требующие внешнего ПЗУ, а иногда и варианты со встроенным РПЗУ (рис. 11.33).

Рис. 11.33. Микроконтроллер с РПЗУ. а — 8-разрядный микроконтроллер с контактами для установки РПЗУ; б — 8-разрядный микроконтроллер со встроенным РПЗУ.

Это дает возможность при разработке прибора использовать вариант с РПЗУ (или внешним ПЗУ), куда можно записать программу, при подготовке же партии приборов обратиться к более дешевым контроллерам с масочным программированием. Другим типом ПЗУ с однократным программированием являются ПЗУ с плавкими перемычками. При выпуске в них все биты установлены, и для сброса требуемых бит ПЗУ надо подвергнуть действию электрического тока. В качестве типичного примера можно привести микросхему Harris НМ6617, КМОП ППЗУ (программируемое постоянное запоминающее устройство) объемом 2Кx8. ППЗУ с плавкими перемычками выпускаются также на базе биполярной (ТТЛ) технологии.

ЭРПЗУ. Электрически стираемые программируемые ПЗУ могут быть выборочно стерты и электрически репрограммированы прямо в той же схеме, где они используются в качестве памяти. Такого рода ПЗУ идеально подходят для хранения констант конфигурации, параметров калибровки и прочей информации, которую нельзя записать в ПЗУ до включения компьютера. ЭРПЗУ, как и РПЗУ, используют технологию МОП с плавающим затвором.

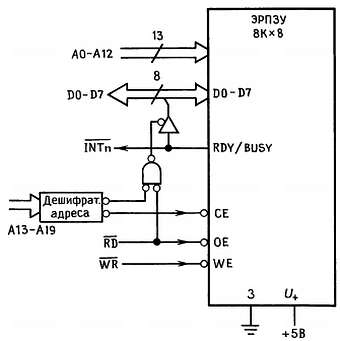

Первые ЭРПЗУ требовали повышенных напряжений и длительной процедуры программирования. Современные микросхемы используют одно напряжение питания +5 В и работают практически так же, как и статические ОЗУ-другими словами, вы можете репрограммировать любой байт с помощью одного цикла записи на магистрали. В микросхеме ЭРПЗУ предусмотрены внутренние цепи для генерации повышенного программирующего напряжения, а внутренняя логика фиксирует данные и генерирует программирующую последовательность длительностью несколько миллисекунд, в которой на время процесса устанавливается флаг BUSY' или в цикле чтения образуются инвертированные данные, чтобы показать, что идет процесс записи. Некоторые ЭРПЗУ реализуют оба этих протокола, обычно называемые "RDY-BUSY" и "DATA'-опрос". Сопряжение с этими ПЗУ осуществляется просто - достаточно подключить их так же, как обычные ОЗУ и использовать линию BUSY' для возбуждения прерываний (либо считывать состояние BUSY' или данных, и использовать его как флаг состояния) (см. рис. 11.34).

Рис. 11.34. ЭРПЗУ.

Протокол DATA' — опроса удобен тем, что ЭРПЗУ можно вставить в стандартный разъем для ОЗУ без каких-либо схемных изменений (разумеется, в ваши программы придется включить строки анализа считываемых назад данных и ожидания их совпадения с тем, что вы записываете). Поскольку запись в ЭРПЗУ выполняется относительно редко, фактически в прерываниях по линии RDY/BUSY' необходимости не возникает.

КМОП ЭРПЗУ выпускаются в виде микросхем с емкостью 2Кx8, 8Кx8 и 32Кx8 по цене примерно 10–50 долл. Время доступа (200–300 нc) и время программирования (2 мс/байт при использовании внутреннего усовершенствования алгоритма) сравнимы с показателями стандартного РПЗУ. ЭРПЗУ, как и РПЗУ, допускают ограниченное число циклов чтения/записи. Хотя производители избегают называть конкретные цифры, можно встретить упоминание о 100000 циклах чтения/записи при 25 °C.

Замечание. Хотя ЭРПЗУ уникальны в том отношении, что допускают репрограммирование в рабочей схеме, их также можно запрограммировать и отдельно от места использования, в программаторе для РПЗУ. Это делает их очень удобными для разработки встроенного программного обеспечения, так как вам не надо ждать полчаса, пока РПЗУ со старой программой прожарится под ультрафиолетовым облучателем.

Имеются два любопытных варианта ЭРПЗУ. Фирмы National, Xicor и др. выпускают маленькие микросхемы ЭРПЗУ в мини-DIP-кopпycax с 8 выводами. Емкость этих схем может составлять от 16x16 до 2Кx8 бит; они работают в режиме последовательного доступа и оснащаются тактовым входом и единственной линией данных. Эти микросхемы трудно использовать без микропроцессора; однако в приборах с микропроцессорным управлением они очень удобны для хранения небольшого количества установочных параметров и проч. Та же фирма Xicor выпускает «электрически стираемый потенциометр (ЕЕРОТ)», остроумное применение электрически стираемой памяти, в которой хранится положение «цифрового контакта». В эту микросхему встроена цепочка из 99 равных по величине резисторов, причем положение отвода от них, устанавливаемое программно, сохраняется в энергонезависимой памяти, входящей в ту же микросхему. Нетрудно представить себе прикладные задачи, в которых желательна автоматическая или дистанционная калибровка некоторого инструмента без механической настройки ручек управления.

Недавно появившаяся модификация ЭРПЗУ, называемая моментальной (flash), сочетает высокую плотность РПЗУ с репрограммированием в рабочей схеме, присущим ЭРПЗУ. Однако моментальные РПЗУ, как правило, не позволяют стирать отдельные байты, как это можно делать с обычными ЭРПЗУ. Так, моментальное ЭРПЗУ Intel допускает только полное стирание (как и РПЗУ), в то время как в микросхеме фирмы Seeq предусмотрено стирание либо посекторное (512 байт), либо целиком. Далее, большинство доступных сейчас моментальных ЭРПЗУ требуют дополнительного отключаемого источника питания +12 В на время стирания/записи, что является слишком дорогой ценой, если вспомнить, что обычные ЭРПЗУ питаются от единственного источника +5 В. Моментальные ЭРПЗУ могут выдерживать от 100 до 10000 программных циклов. Технология производства ППЗУ продолжает развиваться, и мы с любопытством ожидаем, что она нам еще преподнесет; ждите и вы!

Энергонезависимые ОЗУ. РПЗУ удобны для применения в качестве энергонезависимых ПЗУ, однако часто возникает необходимость иметь энергонезависимую оперативную память. Для этого можно использовать ЭРПЗУ, однако для них характерен очень длинный (10 мс) цикл записи (и ограниченное число циклов чтения/записи). Имеются две возможности достичь характерного для ОЗУ времени чтения/записи (100 нc) при неограниченном числе циклов чтения/записи: использовать либо статическое КМОП ОЗУ с резервным батарейным питанием, либо необычную микросхему "NOVRAM" фирмы Xicor, в которой объединены статическое ОЗУ и ЭРПЗУ.

Ранее уже обсуждался вопрос о резервном батарейном питании ОЗУ, которое убивает двух зайцев разом: низкая цена и высокая скорость чтения/записи ОЗУ сочетаются с энергонезависимостью ПЗУ. Разумеется, в этом случае следует использовать КМОП ОЗУ с известным значением критического тока. Некоторые фирмы выпускают «энергонезависимые ОЗУ», размещая в обычном DIP-корпусе вместе с микросхемой КМОП ПЗУ литиевую батарейку и логические схемы переключения питания. В качестве примера можно указать микросхемы фирмы Dallas Semiconductor DS1225 (8Кx8) и DS1230 (32Кx8); эта фирма также выпускает линейку «интеллектуальных разъемов», содержащих батарейку и логические схемы, с помощью которых обычные ОЗУ как по мановению волшебной палочки становятся энергонезависимыми. Учтите, что образованное таким образом энергонезависимое ОЗУ, строго говоря, не бессмертно; срок службы батарейки, а следовательно, и данных, около 10 лет. Как и для обычного статического ОЗУ, здесь нет ограничений на выдерживаемое памятью число циклов чтения/записи.

NO VRAM (NOnVolatile RAM-энергонезависимое ОЗУ) фирмы Xicor сочетает обычное статическое ОЗУ с «теневым» ЭРПЗУ в том же кристалле. Входной сигнал STORE' переносит содержимое ОЗУ в ЭРПЗУ при полной длительности цикла записи 10 мс; извлекаются данные быстрее, за время около 1 мкс. При наличии микросхемы контроля питающих напряжений из серии МАХ690 вы заблаговременно получаете предупреждение и можете сохранить содержимое ОЗУ еще до того, как напряжение +5 В упадет до критического значения. Объявлено, что NO VRAM выдерживают 10000 операций сохранения и, подобно обычным ОЗУ, неограниченное число операций чтения/записи в ОЗУ.

Если сравнивать два описанных варианта энергонезависимых ОЗУ, то вариант с резервной батарейкой представляется в общем предпочтительным, поскольку позволяет использовать любое наличное ОЗУ, если только в нем предусмотрен режим отключения при нулевом токе. Это значит, что вы можете использовать большие ОЗУ последних выпусков, а также, например, выбрать наиболее быстродействующие ОЗУ, если это для вас важно. Хотя батарейки имеют конечный срок эксплуатации, для большинства приложений он достаточен. Для кратковременного (сутки или менее) хранения информации вы можете заменить литиевую батарейку двухслойным конденсатором большой емкости; такие конденсаторы в очень маленьких корпусах с емкостью до фарады и более предлагаются фирмами Panasonic, Sohio и др.

Запоминающие устройства: общая сводка. Рис. 11.35 подытоживает важнейшие характеристики различных типов ЗУ.

Рис. 11.35. Типы запоминающих устройств.

Из показанных на рисунке мы рекомендуем динамические ОЗУ шириной 1 бит для больших матриц памяти с возможностью чтения и записи, статические ОЗУ шириной 1 байт для небольших матриц памяти микропроцессорных систем, РПЗУ для хранения программ и параметров, не требующих перезаписи, и либо ЭРПЗУ (если длительность процесса записи не имеет значения), либо статические ОЗУ с резервным батарейным питанием (для достижения максимального быстродействия по чтению/записи) для энергонезависимого хранения модифицируемых данных.

11.13. Другие микропроцессоры

Как и любой дарвиновский процесс, эволюция микропроцессоров протекала в нескольких расходящихся направлениях. В борьбе за выживание менее приспособленным угрожает опасность вымирания. Примером различающихся эволюционных путей являются процессоры с отдельными командами ввода-вывода и с «вводом-выводом, отображаемым на память». В последнем случае регистры периферийных устройств выглядят просто как ячейки памяти (представителем первого направления является МП 8086, второго - МП 68000)[2]. Далее, можно выделить машины, использующие для большинства арифметических операций не регистры, а память. Другая альтернатива в конструировании микропроцессоров касается использования выводов микросхемы: в некоторых ЦП выводы являются многофункциональными, что позволяет повысить гибкость микросхемы. Различаться могут размеры слов (4, 8, 16 или 32 бит) и стеков, а также элегантность (или полнота) системы команд. Каждое семейство микропроцессоров имеет собственный язык ассемблера (вечный камень преткновения для начинающих). Микропроцессоры обычно выполняются по КМОП-технологии, но можно найти и такие, которые используют nМОП-технологию или биполярную логику.

Еще большие различия можно обнаружить у микропроцессоров, предназначенных для решения разных задач. С одной стороны, имеются «однокристальные» процессоры со встроенными ОЗУ и ПЗУ, параллельными портами, УСАПП, таймерами и даже аналого-цифровыми преобразователями. Другая крайность представлена мощными 32-разрядными ЦП 80486, 68040 и АМ29000, которые перекрывают вычислительные возможности больших компьютеров, но для полной реализации своих совершенных качеств требуют обширного аппаратного и программного обеспечения. Микросхемы повышенной степени интеграции занимают золотую середину; например, микросхема Н16 представляет собой комбинацию в одном кристалле ЦП 68000 с двумя УСАПП, таймерами и каналами прямого доступа.

В настоящей главе во всех примерах использовался МП 68008, но мы не хотели бы оставить у читателя впечатление, что другие микропроцессоры хуже. В табл. 11.8 перечислены наиболее популярные из доступных в настоящее время микропроцессоров. Таблицу нельзя рассматривать, как исчерпывающий список всего имеющегося в продаже.

11.14. Эмуляторы, системы проектирования, логические анализаторы и макетные платы

Если вы разрабатываете прибор с микропроцессорным управлением, то каким образом выполнить написание, ассемблирование, отладку и загрузку в ПЗУ программы для него? Это серьезная проблема, особенно для начинающих работать с микропроцессорами. Для решения ее можно предложить целый ряд методик, от простого автономного способа под названием «прожги и ломай» (burn and crash) до изощренных систем проектирования и эмуляторов языков высокого уровня. В настоящем разделе мы попытаемся описать, чем можно сегодня воспользоваться и насколько это полезно при разработке приборов с микропроцессорным управлением.

«Прожги и ломай». Это красочное название описывает простейший способ разработки программы для микропроцессорной аппаратуры. Заключается он в следующем. Сначала с помощью ассемблера или компилятора на компьютере общего назначения (возможно вашей настольной машине) вы получаете коды выполнимой программы, которые можно записать в РПЗУ. Если процессор-мишень, т. е. микропроцессор разрабатываемого прибора отличается от процессора использованного компьютера, вам понадобится «кросс-ассемблер»; в противном случае можно воспользоваться «родным» ассемблером компьютера. Теперь можете запрограммировать РПЗУ (это «прожги») и испытать программу в вашем приборе (это «ломай»). Дальнейшая отладка заключается в обнаружении неправильностей, вызванных ошибками в программе (или в аппаратуре), исправлении программы или включении в нее диагностических тестов, и повторных испытаниях. Поиск ошибок — широкое поле для остроумных приемов. Например, вставив в отлаживаемую программу соответствующие строки, вы можете использовать ЭЛД-индикаторы или другие порты в диагностических целях, выводя информацию о том, что происходит в программе. Не забывайте и о традиционных инструментах мира электроники — логическом пробнике, осциллографе, а также (в минуту отчаяния) о логическом анализаторе (см. ниже).

Заменители ПЗУ. Методика «прожги и ломай», описанная выше, является медленной процедурой. Хотя иногда она адекватна стоящей перед вами задаче, вам, скорее всего, быстро надоест повторение одних и тех же операций стирания РПЗУ под ультрафиолетовой лампой и программирования его в программаторе. Можно предложить способы ускорения этой процедуры: (а) Вместо РПЗУ используйте ЭРПЗУ. Программируются они не быстрее, но зато не надо тратить столько времени на стирание, (б) Используйте на время разработки не РПЗУ, а КМОП ОЗУ с резервным батарейным питанием (энергонезависимое). Эти микросхемы столь же быстры, как и обычные ОЗУ (т. е. «программируются» мгновенно) и имеют выводы, совместимые с РПЗУ, так что их можно вставлять в панельку разрабатываемого вами прибора, предназначенного для установки ПЗУ с программой. ОЗУ с резервным батарейным питанием поставляют многие фирмы (Dallas, Thomson-Mostek и др.); можно их сделать и самим, (в) Используйте «эмулятор ПЗУ». Это небольшая коробочка с кабелем и 28-контактным разъемом DIP на конце. Разъем вставляется в панельку для РПЗУ в вашем приборе, и коробочка эмулирует ПЗУ. Фактически, однако, она содержит двухпортовое ОЗУ, которое вы загружаете из вашего компьютера через последовательный порт. Использование эмулятора ПЗУ обеспечивает максимальную скорость отладки; так как для изменения программы вам не надо каждый раз вынимать и вставлять микросхемы памяти — вы просто загружаете новую программу в эмулятор, который остается включенным в налаживаемый прибор. Эмуляторы ПЗУ выпускаются под названиями "Memulator" или "Romulator" (последний поставляется фирмой Onset Computer Corp., Норт-Фалмут, Миннесота).

ПЗУ-монитор. Если в вашем приборе имеется последовательный порт, можно упростить процедуру разработки программного обеспечения, запрограммировав небольшое РПЗУ — «монитор», задачей которого является не управление прибором, а лишь обеспечение связи между памятью и портом. Простейший монитор позволяет загрузить в ОЗУ программу и запустить ее выполнение. Это заметно ускоряет разработку программного обеспечения, потому что пробные программы можно загружать в ОЗУ прибора непосредственно из компьютера. Не составляет особого труда расширить функции монитора, например, чтобы он мог считывать содержимое указанных ячеек ОЗУ. С таким добавлением пробные программы получают возможность сообщать о том, что происходит, например, путем засылки чисел в определенные ячейки ОЗУ перед возвратом управления монитору (через который компьютер может проанализировать содержимое этих ячеек). Такой монитор позволяет включить в пробную программу «программные точки останова», в которых содержимое требуемых регистров или ячеек памяти копируется в неиспользуемую область ОЗУ, откуда затем считывается через монитор в компьютер. ПЗУ-монитор заметно сокращает длительность разработки, так как помогает вам быстро находить причину неправильной работы программы.

Аппаратный эмулятор. Способ «прожги и ломай», как и его усовершенствования, описанные выше, часто позволяют решить поставленную задачу. Однако этот способ не идеален. Во-первых, он требует использования дополнительных ресурсов, таких, как последовательный порт. Во-вторых, и это более важно, он не обеспечивает обнаружения ошибочных операций на аппаратном уровне. Чтобы понять это последнее утверждение, представьте себе, что в вашем приборе возникает отказ, потому что он неправильно пытается записывать в РПЗУ. Это вы уже поняли, однако дальше дело застопорилось, так как трудно с помощью программной точки останова локализовать ошибку, обнаруживаемую только аппаратно. В нашем примере ошибка могла заключаться в затирании содержимого регистра. Это весьма неприятная ошибка: сбой происходит спустя значительное время после инициировавшего затирание события, и понять, в чем дело, изучая текст программы, нельзя. В таких случаях вам требуется поставить «аппаратную точку останова».

Решение лежит в использовании аппаратного эмулятора. Это коробка (или вставляемая плата) с аппаратными средствами, эмулирующая на этот раз микропроцессор вашего прибора. Она подсоединяется к налаживаемому прибору посредством кабеля, имеющего на конце разъем, имитирующий ЦП. Аппаратный эмулятор может выполнять как программу, находящуюся в памяти налаживаемого прибора (РПЗУ или ОЗУ), так и программу, загружаемую вами в эмулятор. В любом случае эмулятор осведомлен обо всем, что происходит в ЦП; он может следить за содержимым регистров, а также устанавливать аппаратные точки останова. Например, для решения нашей гипотетической проблемы можно потребовать от эмулятора, чтобы он фиксировал циклы записи в адресное пространство, занимаемое РПЗУ, и выдавал дамп регистров и листинг последних 100 команд, выполнявшихся перед неправильной записью в РПЗУ.

Аппаратная эмуляция является наилучшим средством разработки программ, обеспечивая максимальную гибкость и скорость работы. К ее недостаткам следует отнести высокую стоимость (несколько тысяч долл., иногда гораздо больше) и необходимость приобретать новый эмулятор для каждого типа используемого вами микропроцессора. Эмулятор ПЗУ, для сравнения, не является «процессорно-зависимым», но и уступает аппаратному эмулятору по своим возможностям. Это, так сказать, аппаратный эмулятор бедняка.

Системы разработки. «Система разработки» — это обобщенный термин для комбинации кросс-ассемблера, программатора РПЗУ и аппаратного эмулятора. Традиционно такие средства выпускались в виде внушительных автономных систем, однако в настоящее время большую популярность завоевывают вставные платы, использующие компьютер в качестве вычислительной базы, и, возможно, управляющие внешним блоком, содержащим дополнительные схемы. Как бы они не выглядели, вам необходимо приобрести такого рода систему, если вы специализируетесь на разработке микропроцессорных устройств, ориентированных на конкретный микропроцессор. Обычно системы разработки предлагаются фирмами, выпускающими микропроцессорные семейства. Некоторые фирмы, кроме того, изготавливают «универсальные эмуляторы», в которые можно вставлять платы с микропроцессорами разных типов. Системы разработки выпускаются, в частности, фирмами Hewlett-Packard, Tektronix, Microcosm, Applied Microsystems.

Логические анализаторы. Логические анализаторы можно назвать «супер-осциллографами» для разработки цифровой аппаратуры. Логический анализатор выступал в качестве главного действующего лица в книге Трейси Киддера «Душа новой машины». Эти замечательные устройства выглядят, как странные осциллографы, но в действительности включают в себя десятки каналов, большие объемы памяти, сложную логику «распознавания слов», а также средства деассемблирования выполняемых команд и представления их на экране. Логический анализатор может работать в двух режимах: анализа состояний и временного анализа. Вот как вы их должны использовать.

Анализ состояний. В этом режиме на вход статического анализатора подается синхронизирующий тактовый сигнал от вашей схемы (обычно тактовый сигнал ЦП), а сонм выводов (торчащих из анализатора) подключается к линиям данных и адреса, а также к другим интересующим вас сигналам. Хороший логический анализатор обслуживает 60–80 каналов при тактовой частоте до 25 МГц или больше. Затем вы устанавливаете сигнал запуска так, чтобы зафиксировать интересующее вас программное событие. Обычно в анализаторе имеется несколько регистров распознавания слов, в которые вы можете вводить любую последовательность 0,1 и X (произвольное состояние); это, разумеется, биты адреса и данных. В хорошем логическом анализаторе предусматривается возможность комбинирования выходов регистров распознавания слов в виде булевых выражений и функций состояния; например, можно образовать сигнал запуска от десятого прохода некоторой подпрограммы.

Логический анализатор ожидает сигнала запуска, затем запоминает последовательность состояний всех входных линий. Их можно наблюдать в виде цифрового сигнала или как последовательность нулей и единиц (либо шестнадцатеричных или восьмеричных чисел), рядом с которыми приводятся результаты деассемблирования. Вы можете просматривать массив запомненных состояний (обычно 4К или больше) и, что особенно важно, двигаться по нему от сигнала запуска «назад во времени». Это дает возможность проанализировать несколько тысяч состояний, предшествующих сигналу запуска, что, как правило, позволяет найти источник неприятностей.

Временной анализ. В режиме временного анализа логический анализатор работает от асинхронного тактового сигнала высокой частоты, обычно 100 МГц, который фиксирует логические состояния меньшего числа входных линий (чаще всего 16). Логика запуска поневоле проще и допускает обычно лишь одно слово распознавания. Анализатор ожидает установленного условия запуска, после чего заполняет свою память быстрыми выборками. В режиме временного анализа вы можете наблюдать кратковременные выбросы и другие искажения формы сигнала, которые незаметны в режиме анализа состояний. Можно перейти в режим «обнаружения выбросов», когда анализатор ищет два перепада, возникающих в течение 10 нc — периода дискретизации.

Перекрестный запуск. Объединение анализа состояний и временного анализа дает мощную методику, называемую перекрестным запуском. В этом комбинированном режиме анализ состояний может инициировать временной анализ и наоборот. Так, вы можете настроить логику запуска, чтобы она фиксировала заданное состояние в конкретном программном цикле и запускала временной анализ, который после обнаружения заданного слова (условия) запуска записывает в память пакет данных. Таким образом удается обнаруживать короткие выбросы логического происхождения, возникающие редко.

Логические анализаторы с перекрестным запуском образуют расщепленный информационный кадр, что дает возможность, просматривая состояния, наблюдать также и форму сигналов. В области логических анализаторов наиболее известны имена Gould, Hewlett-Packard, Philips и Tektronix.

Макетные платы. В 70-х гг., когда широкую популярность стали завоевывать 8-разрядные микропроцессоры, такие, как 6800 и Z80, для каждого нового микропроцессора выпускалась макетная плата. Это был набор аппаратуры, куда входили небольшая клавиатура, шестнадцатеричный дисплей, ПЗУ, РПЗУ-монитор, несколько параллельных и последовательных портов, а также собственно плата для монтажа на ней схем, добавляемых пользователем. Вы могли, выполнив ручное ассемблирование небольшой программы, ввести ее посредством клавиатуры и наслаждаться результатом. Для инженерного мира, начинающего осваивать микропроцессоры, макетные платы предоставляли простой способ приобретения знаний и навыков.

Теперь инженерный мир стал более искушенным, и макетные платы почти вымерли. Однако и сейчас можно встретить в продаже макетные платы для специализированных процессоров, например БИС обработки сигналов или сложных видеопроцессоров. Такие платы содержат сам процессор, окруженный «склеивающей» логикой и аналоговыми компонентами для обработки сигналов, а часто и обычный микропроцессор, используемый для управления. Современные макетные платы обычно выполняются в виде вставных плат для персональных компьютеров и комплектуются необходимым программным обеспечением. Если принять во внимание сложность современных процессоров специального назначения, макетные платы экономят массу времени и вполне оправдывают свое существование.

Более 800 000 книг и аудиокниг! 📚

Получи 2 месяца Литрес Подписки в подарок и наслаждайся неограниченным чтением

ПОЛУЧИТЬ ПОДАРОК