Быстродействующие ключи

Те же самые эффекты, которые ограничивают возможности линейных высокочастотных усилителей (ёмкости переходов, ёмкость обратной связи (проходная) с её эффектом Миллера, а также паразитные емкости в комбинации с конечными сопротивлениями источника и нагрузки), налагают ограничения по скорости и на быстродействующие цифровых схемы. Многие из этих проблем непосредственно конструктора не касаются, поскольку они удачно разрешены при построении самой цифровой ИМС. Трудности возникают при использовании схем ТТЛ, например, только если в конструкции требуются дискретные транзисторы. Тем не менее часто необходимо знать, как работают быстродействующие переключающие схемы. Например, при работе на внешнюю высоковольтную или сильноточную нагрузку (или нагрузку, требующую ток противоположной полярности) от логического выхода очень легко может ухудшиться быстродействие (например, раз в 100), если при конструировании допустить небрежность. Более того, бывают ситуации, когда используются бескорпусные цифровые логические схемы и вам приходится все делать самому.

Этот раздел мы начнем с рассмотрения простых моделей транзисторов, полезных при расчете схем переключения. На нескольких примерах покажем, как эти модели работают (и как важно правильно подобрать транзистор). В заключение рассмотрим построение транзисторных переключающих схем на примере одной быстродействующей схемы (фотоумножительный предусилитель — дикриминатор).

13.23. Модель транзистора и ее уравнения

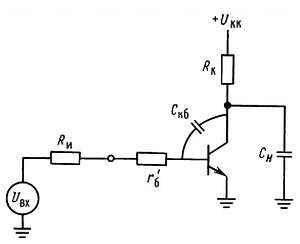

На рис. 13.50 изображена ключевая схема на насыщенном транзисторе, включенном инвертором, сигнал на которую подается от источника импульсов с чрезвычайно короткими временами нарастания и спада, ^-сопротивление источника, r'б — относительно небольшое внутреннее распределенное сопротивление базы транзистора (около 5 Ом), Скб — наиважнейшая емкость обратной связи (проходная) и RK — сопротивление нагрузки, имеющей емкость Сн.

Рис. 13.50.

Эффекты, связанные с конечной величиной нагрузочного сопротивления, можно учесть, если считать, что RK представляет собой суммарное сопротивление при соответствующем пересчете UKK. Емкость между коллектором и эмиттером входит в Сн, а Сбэ не учитывается, поскольку благодаря эффекту Миллера Скб всегда доминирует на входе.

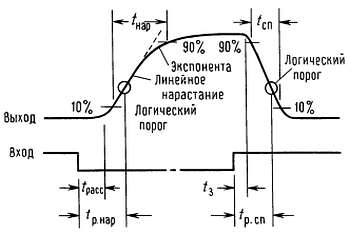

На рис. 13.51 изображена типичная для этой схемы форма выходного импульса, если на вход ее подается хорошо сформированный отрицательный сигнал.

Рис. 13.51. Форма импульса на выходе транзисторного ключа.

Время нарастания tнap определяется как промежуток между моментами времени, когда значение сигнала равно соответственно 10 и 90 % конечного значения. Так же определяется и время спада tсп. Особо отметим относительно длительный период рассасывания неосновных носителей в базе tрасс, который требуется, чтобы транзистор из насыщения перешел в линейное состояние проводимости, по сравнению с соответствующим более коротким временем задержки t3, требующимся для выхода из состояния отсечки. Эти параметры общепринято брать между 10 %- и 90 %-ными точками. В цифровой логике более полезно знать времена распространения tр.нар и tр.сп, определяемые как времена от момента изменения состояния входа до момента, когда выходной сигнал проходит через логический порог (соответственно на нарастающем и спадающем фронтах). Для этих величин обычно пользуются другими обозначениями, например, t1.0з.др и t0,1з.др.

Попробуем применить модель схемы для определения времени нарастания и спада в данной цепи. В процессе расчета станет понятным, почему нарастающий фронт выходного сигнала иногда заканчивается по экспоненциальному закону.

Определение времени нарастания. После перехода входного сигнала в состояние низкого уровня и окончания — времени tрасс напряжение на коллекторе начинает возрастать. Два эффекта ограничивают скорость нарастания: a) RK в сочетании с Скб и Сн дают постоянную времени, определяющую экспоненциальный рост напряжения до UKK, но б) если скорость этого роста достаточно велика, получающийся в результате ток через Скб, выделяясь на сопротивлении источника (Rи + r'б), вызывает прямое смещение базы, и оно может возбуждать базу, что тормозит рост коллекторного напряжения (отрицательная обратная связь). Если это происходит, то схема оказывается интегратором, а сигнал на коллекторе — линейно нарастающим. В целом (в зависимости от параметров схемы и самого транзистора) импульс на коллекторе сначала имеет линейное нарастание, переходящее затем в экспоненту, как показано на рис. 13.51.

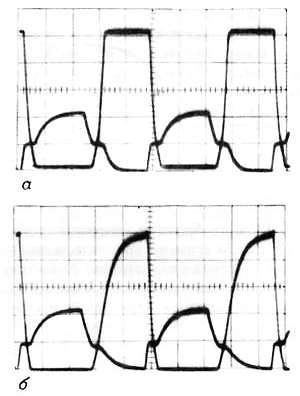

На рис. 13.52 приведены осциллограммы этих эффектов.

Рис. 13.52. Импульсы переключения напряжений затвора и стока. а — сопротивление стока 10 кОм; б — сопротивление стока 200 кОм. Видно, как с источником, имеющим преувеличенное сопротивление 100 кОм, динамический эффект Миллера способствует фиксации уровня. Цена деления по вертикали 2 В/дел.; частота сигнала 6 кГц.

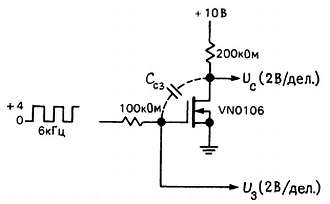

Вместо n-p-n-транзистора мы воспользовались n-канальным полевым МОП-транзистором, работающим в режиме обогащения. Он ведет себя также, но большее напряжение отпирания затвора существенно улучшает форму импульсов. Кроме того, полевые МОП-транзисторы не имеют эффектов, связанных с временами рассасывания носителей и задержки, и у них отсутствует постоянный входной ток, при котором все упрощается. На рис. 13.53 приведена схема, в которой импеданс источника сигналов нами намеренно сделан преувеличенным.

Рис. 13.53.

Заметьте, как емкость обратной связи поддерживает напряжение затвора на уровне порога отпирания во время переключения стока. Обратите внимание также на то, что нарастание сигнала стока изменяется экспоненциально, если Rc велико.

Простой способ расчета поведения схемы состоит в следующем:

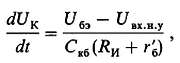

1. Рассчитывается скорость нарастания напряжения на коллекторе для «ограничения вследствие интегрирования» с использованием уравнения

где Uвх.н.у — низкий уровень входного напряжения.

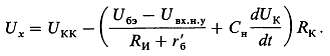

2. Определяется коллекторное напряжение Ux, при котором выходное напряжение переходит от линейного нарастания к экспоненте из уравнения

С помощью этих двух уравнений можно вычислить форму переднего фронта коллекторного импульса и время нарастания. Если Ux окажется отрицательным, то это означает, что нарастание коллекторного напряжения носит чисто экспоненциальный характер: емкостная нагрузка преобладает и ток через емкость обратной связи вообще не возбуждает базу. Величина r'б обычно незначительна.

Упражнение 13.1. Выведите две предшествующие формулы. Указание: для вывода второй формулы приравняйте ток обратной связи, текущий в базу, к току коллекторного резистора за вычетом тока, ответвляющегося в емкостную нагрузку.

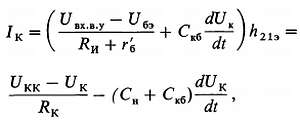

Определение времени спада. По истечении короткого времени задержки t3 после перехода входного сигнала в состояние высокого уровня Uвх.н. у коллекторное напряжение начинает падать к уровню насыщения транзистора. Произведя несложные расчеты, легко увидеть, что ток коллектора определяется выражением

где первое выражение — это ток базы, умноженной на h21э, а второе — ток коллектора, определяемый как ток через RK минус ток, отбираемый зарядом емкости, подключенной к коллектору.

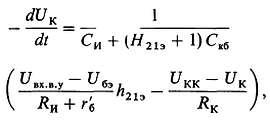

Напоминаем, что dUK/dt отрицательно. После преобразования получим

где первый член в скобках соответствует току управления в цепи базы, умноженному на h21э, а второй — току через коллекторный резистор. Теперь вы можете попробовать рассчитать некоторые схемы; вы сможете определить времена нарастания и спада, а также какая емкость доминирует. Сначала, однако, рассмотрим времена рассасывания носителей и задержки.

Времена задержки и рассасывания носителей в базе. Обычно времена задержки очень малы. Главную роль играет постоянная времени, которая определяет снижение заряда емкости базы до Uбэ и равна в общем

Т ~ (Rи + r'б)(Скб + Сбэ).

При очень высоком быстродействии влияние постоянных времени транзисторных переходов может оказаться важным. Гораздо большую роль играет время рассасывания. У транзистора в насыщении заряд накапливается в области базы, и после того, как управляющий сигнал на базе становится близким к потенциалу земли (или даже отрицательным), требуется относительно длительное время, чтобы ранее инжектированные из эмиттера избыточные неосновные носители ушли из базы под действием тока коллектора. Транзисторы сильно отличаются друг от друга по времени рассасывания; это время можно сделать короче, если уменьшить ток базы во время насыщенного состояния и если при запирании подавать обратное смещение на базу, чтобы обеспечить обратный ток базы, когда транзистор переключается в состояние отсечки. Эти моменты отражены в уравнении для времени рассасывания tрасс:

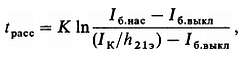

где обратный ток базы Iб. выкл отрицателен при токах базы, обеспечивающих «разряд» заряда в базе. Коэффициент К определяется «временем жизни неосновных носителей», которое сильно уменьшается при легировании золотом. Однако такое легирование уменьшает h21э и увеличивает ток утечки. Этим объясняется высокое быстродействие ТТЛ, а также их низкое напряжение пробоя (порядка 7 В). Времена рассасывания могут быть очень большими и составлять несколько сотен наносекунд, что примерно на порядок превышает времена задержки при включении. Так, например, распространенный прибор общего назначения 2N3904 имеет максимальное время задержки 35 нc, а время рассасывания 200 нc при стандартных условиях проверки, когда на базу подается отрицательное смещение, равное падению напряжения на двух прямосмещенных диодах. Поскольку времена рассасывания существенно ограничивают быстродействие переключательных схем, приходится применять меры для решения проблемы насыщения.

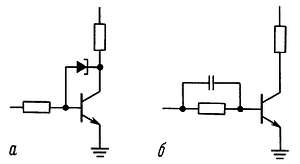

Один из способов заключается в том, чтобы исключить вовсе состояние насыщения у транзистора. Включенный в обратную связь диод Шоттки («связь Ваker'a») между базой и коллектором прекрасно выполнит эту задачу, отбирая избыточный ток базы, когда транзистор близок к насыщению и потенциал коллектора ниже, чем у базы. Это предотвращает насыщение транзистора, так как напряжение прямосмещенного диода Шоттки меньше напряжения прямосмещенного перехода коллектор-база. Этот метод использован в ТТЛ-логических схемах с диодами Шоттки (ТТЛ-Ш). Часто небольшой «ускоряющий» конденсатор (25-100 пФ), параллельный резистору в цепи базы, хорошо дополняет этот прием, поскольку способствует уменьшению времени рассасывания, обеспечивая дополнительные импульсы тока, способствующие «разряду» базы, когда транзистор насыщен, а также быстрому нарастанию тока базы, когда транзистор включается. Эти схемы показаны на рис. 13.54.

Рис. 13.54. Схемы ключей с повышенным быстродействием. а — с диодом Шоттки; б — с ускоряющим конденсатором.

13.24. Устройства аналогового моделирования

Очевидно, что проектирование как высокочастотных усилителей, так и быстродействующих ключей, сложная тема, особенно при полном наборе эффектов, вызываемых присущими им паразитными емкостями и индуктивностями. Наши упрощенные модели дают возможность хорошо прочувствовать схему, но они часто могут быть неадекватными, если вы попытаетесь выжать максимально удовлетворительные характеристики из усилителей, например, в области ГГц. Традиционное приближение состоит из сочетания более сложного моделирования (подкрепленное значительными расчетами!) и большого количества макетных плат.

Приятные разработки получаются с использованием уже развитых систем автоматического аналогового моделирования, в частности программы, называемой "SPICE" и ее некоторых коммерческих расширений. SPICE (автор L. W. Nagel) моделирует работу вашего опытного варианта схемы (используя библиотеку усложненных моделей элементов), предсказывает коэффициент усиления, искажения, шумы, частотный отклик и т. д. Вы можете попросить систему показать форму сигнала (напряжения и тока) в любой точке схемы — компьютерный осциллограф! Таким образом, вы можете проигрывать различные варианты вашей гипотетической схемы, увеличить быстродействие конденсаторов, проводить испытания элементов, делать замены в схеме и т. д. Фактически, при хорошем моделировании можно исследовать влияние допустимых отклонений параметров элементов путем либо обычного анализа сбоев, либо проводя более сложную статистическую обработку методом «Монте-Карло». Некоторые программы моделирования выполняют также анализ «чувствительности», который указывает вам элементы, в наибольшей степени определяющие характеристики схемы.

Программы автоматического моделирования недороги и приспособлены для настольных компьютеров так же как и для любой большой вычислительной системы (например, IsSpice фирмы Intusoft или PSpice Microsim). Наибольшее признание получили таблицы соединений ("netlist") — продукт программ создания чертежа схемы ("Schematic capture") (разд. 12.08). Программы моделирования не ограничены проектированием высокочастотных схем. Они применимы и к моделям операционных усилителей, цифровых схем и внутренностей самой ИМС. Хотя SPICE пока доминирует, но уже появилось около дюжины программ моделирования, оптимизированных под конкретные применения.

Более 800 000 книг и аудиокниг! 📚

Получи 2 месяца Литрес Подписки в подарок и наслаждайся неограниченным чтением

ПОЛУЧИТЬ ПОДАРОК